Other Parts Discussed in Thread: CDCI6214, CDCE6214

主题中讨论的其他器件: CDCE6214

工具与软件:

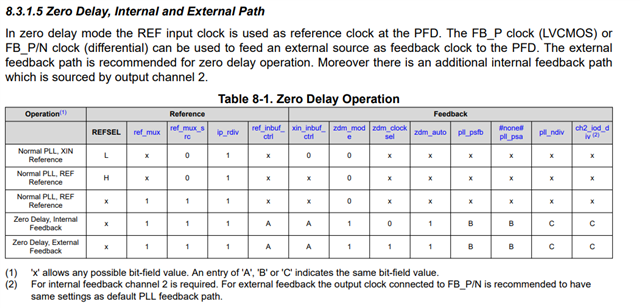

使用 REFP/N 作为基准时、我可以看到输出时钟和输入基准之间的相位看起来取决于基准频率。

我想我已经正确地对 PLL 进行了编程;我已将 ip_rdiv 设置为1;我正在设置 pll_ndiv 和 pll_psfb 以获得允许范围内的 f_vco。 我的输入频率在1和100 MHz 之间。 我设置了 SYNC_EN 位。

当我更改输入频率时、我根据需要应用新的 PLL 参数并进行重新同步。 我观察到的是、基准时钟和输出时钟之间的相对相位在很大程度上取决于频率。

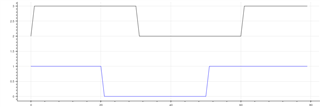

为了说明、当输入时钟为5 MHz 时、我得到:

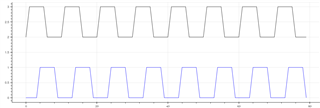

如果是30 MHz、我会得到以下消息:

顶部(黑色)是输入基准、底部(蓝色)是 PLL 输出时钟。 在本例中、输出频率=输入频率、但这只是为了更好地说明该问题;在我的应用中、情况并非总是如此。

当我增加基准频率时、相位偏移以非常规律的单调方式移动。

PLL 已锁定(声称是、似乎是)、并且这是100%可重现的(对于给定的频率、我始终获得相同的相位)。

这是预期行为吗? 我可以做什么来获得固定相位关系吗?

我知道可以使用输出 SYNC_DELAY 功能、但我认为这不是完整的解决方案、因为调节非常粗略并且范围有限。