工具与软件:

您好!

我对 PLLatinum 仿真有疑问。

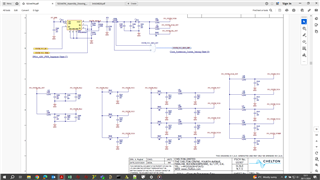

我们在 PLLatinum 仿真中使用具有外部 VCXO 选项的 LMK04828B、为 PLL1和 PLL2提供了以下值、并且使用与 CPout1和 CPout2连接的滤波器值相同的值、如下所示。

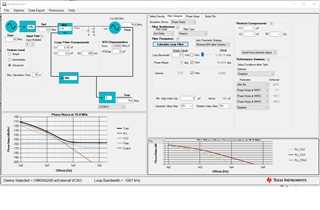

但具体而言、当我为器件加载外部 VCXO 时、PLLatinum Sim 加载 KVCO 和 VCOCap 值、如下所示(电荷泵电流(KPD)、输入和输出频率是我们目前在设计中使用的值、因此是正确的)。

如 上所示加载 PLLatinum Sim 时、默认 KVCO 值为0.0025 MHz PLLatinum/V。

如 上所示加载 PLLatinum Sim 时、默认 VCOCap 值为0pF。

但是、由于我们使用的是外部 VCXO、我在下面提到了它的数据表链接:

查看外部 VCXO 数据表后、我更改了 VCO 特性值(KVCO 和 VCOCAP) 、如下所示。

我已将25ppm 调谐灵敏度转换为 Hz (来自 VCXO 数据表)、并在 KVCO 字段中使用了该值、我认为 VCOCap 将是输出电容、使用了 VCXO 数据表中的15pF、并将其放置在下面的 VCOCap 字段中。

使用这些值后、我们得到与默认值不同的 loop filer 二阶值、我们在设计中使用这些值。

我现在有以下问题、

1.我们是否只是将 KVCO 和 VCOCap 值保留为在选择了带有外部 VCXO 的 LMK04828后 PLLatinum SIM 首次加载时的值不变?

如何获得 VCOCap 值?

3.我如何通过更改第二个屏幕截图中显示的 KVCO 和 VCOCap 值来查找环路滤波器值? 我该怎么做才能使它正确?

谢谢!