工具与软件:

您好、TI

我们正在设计一个 clk 分频器解决方案,详细要求是将 LVCMOS18 76.8MHZ (单输入)REFCLK 分为 LVCMOS18 38.4MHZ (低 附加抖动<500fs)(单输出);

LVCMOS18是否可以用作时钟输入 ? 当 LVCMOS 作为时钟输入源时、交流/直流规格是多少?

非常感谢~

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Alex、

我们并不提供 LVCMOS 用作时钟输入源时的交流/直流规格;但是、您可以通过将 LVCMOS 信号输入到同相输入引脚并将另一个输入引脚偏置为共模电压、将 CDCM1802配置为接受 LVCMOS。 最简单的方法是使用等效电阻器将引脚上拉至 VDD、然后下拉至 GND (另外还向 GND 添加一个去耦电容器、与下拉电阻器并联)。

谢谢!

Michael

你(Michael)好

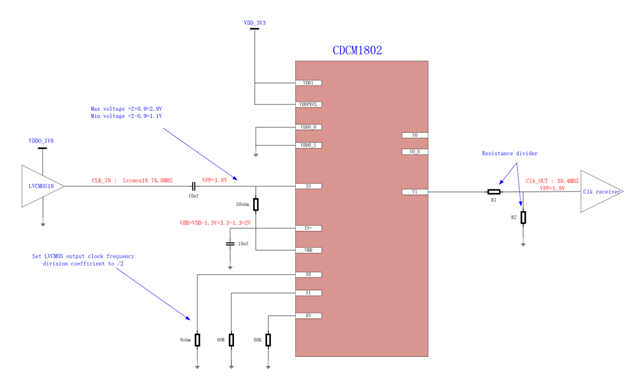

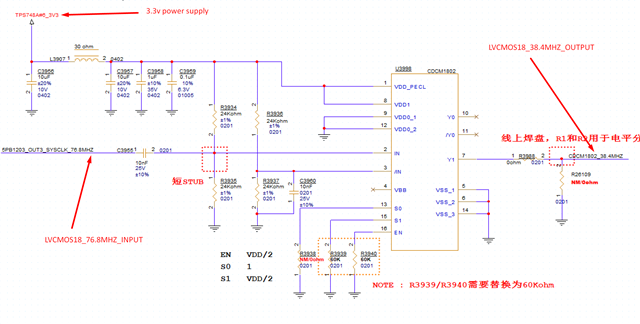

如上所示、使用 CDCM1802将76.8MHZ LVCMO18时钟更改为38.4MHZ LVCMOS18时钟

(1) 输入时钟为 LVCMOS18 、 Vpp=1.8V 、偏置电压 bia VBB 电源

(2) 输出时钟也是 LVCMO18、Vpp=1.8V

有几个问题要问:

(__LW_AT__1 μ s)上述方案的方框图是否有任何问题?

(__LW_AT__2)使用 LVCMOS 输入时的 VIL 和 VIH 范围是多少?

你(Michael)好

如果使用 VBB(CLK=3.3-1.3=2V、提供偏置电压 、VBB 最小电压为2-0.9=1.1V)且 VIL 阈值= CLK/2-0.5=3.3/2-0.5=1.15、则电压裕度相对较低、我要 按如下方式优化原理图 :VDD 最小电压=1.65-0.9=0.75V

(__LW_AT__1) 以上方案是否有任何问题?

(__LW_AT__2)VBB、Y0、/Y0 信号引脚是否可以保持悬空?

非常感谢~