主题中讨论的其他器件:LMK00804B、

工具与软件:

尊敬的:

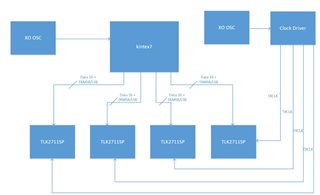

我将 TLK-2711SP 与 kintex7 FPGA 一起使用 、如下所示。

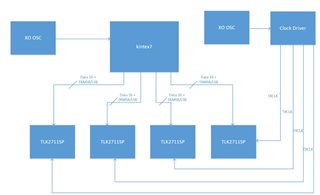

遗憾的是、FPGA 时钟具有较差的抖动特性。 所以、我想我要尝试如下图所示进行设计。

如何使时钟和数据的时序相匹配?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的:

我将 TLK-2711SP 与 kintex7 FPGA 一起使用 、如下所示。

遗憾的是、FPGA 时钟具有较差的抖动特性。 所以、我想我要尝试如下图所示进行设计。

如何使时钟和数据的时序相匹配?

此致、

您好、Dean:

由于时钟信号的上升沿用于对数据信号进行采样、因此 TXCLK 输入应与 TXD 数据输入同步。 因此、我认为不可能使用第二个振荡器作为 TXCLK 输入、因为随着时间的推移、它可能会偏离数据信号的时钟域。

FPGA 时钟输出是否满足这些要求? 如果是、我建议坚持使用此设计。

如果不能、是否可以从 FPGA 外部缓冲或分离同一个振荡器? 我假设 FPGA 数据输出与其基准时钟输入同步。

此致!

卢卡斯

您好、Dean:

为了更好地了解时钟缓冲器抖动和偏斜规格、我查看了 LMK00804B、这是一款 TI 扇出缓冲器、我认为可与 TLK2711-SP 配合使用。 该器件的典型附加抖动为40fs RMS、 明显小于40ps p-p 的 TLK 参考时钟抖动要求 此外、该器件的最大 传播延迟为2.2ns、最大输出偏斜为35ps。 TLK 的最大基准时钟频率为125 MHz、相当于最小周期8ns。 这意味着时钟缓冲器的偏斜规格不应对 TLK 的性能产生负面影响。 由于 TLK 在基准时钟的上升沿对数据信号进行采样、因此我们只需要确保数据信号不会与上升沿同时转换。

请注意、我不是时钟器件方面的专家。 如果您对 TI 的时钟和计时器件有更详细的问题、请发布新的 E2E 论坛问题、我们将为您的主题分配一名负责的工程师。

我确实有几个问题来确认这种类型的设计应该有效。

此致!

卢卡斯