工具与软件:

你(们)好

我在 设计中使用 TI LMK5C33216、 想要查找有关锁相机制的更多信息、我想了解以下内容:

1.哪里能找到关于锁相电路的更多信息? 也许还有应用手册?

2.对于 LOPL、器件是否像在 LOFL 情况下那样重新开始获取输入(移至保持和...) )。

3、要使 输出时钟相位 固定到输入端、必须使用 ZDM、对吗?

4.如果 输入时钟相位在改变、那么在我看不到 LOPL 的情况下、输出时钟的行为将是什么?

THX:

HAIM

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

你(们)好

我在 设计中使用 TI LMK5C33216、 想要查找有关锁相机制的更多信息、我想了解以下内容:

1.哪里能找到关于锁相电路的更多信息? 也许还有应用手册?

2.对于 LOPL、器件是否像在 LOFL 情况下那样重新开始获取输入(移至保持和...) )。

3、要使 输出时钟相位 固定到输入端、必须使用 ZDM、对吗?

4.如果 输入时钟相位在改变、那么在我看不到 LOPL 的情况下、输出时钟的行为将是什么?

THX:

HAIM

嗨、Haim:

我们建议使用经过改进的较新版本 LMK5C33216 A. 这具有更好的抖动性能并增加了 HCSL 功能。 引脚排列保持不变、但有些寄存器会发生变化。

这有什么帮助吗?

此致、

Jennifer

Jennifer、您好!

感谢快速的响应。

在 DPLL 是频率锁定(LOFL=0)的情况下、我们假设在一段时间后、输入时钟相位超出阈值(LOPL=1)、但频率重新确定相同(LOFL=0)、正确的说法是、在这种情况下不会发生任何情况、输入相位将传输到输出端、只有在频率发生变化时、器件才会进入保持模式。 对吗?

当使用 ZDM 时 、唯一的变化将是 输入时钟相位、 输出相位将是什么?

请告知:

THX:

HAIM

嗨、Haim:

新年快乐!

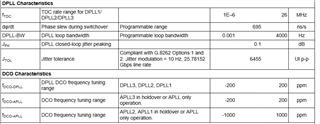

如果 DPLL 基准被视为有效基准、则在正常运行期间 LOFL=0、LOPL=1、DPLL 将保持激活状态并继续跟踪输入。 如果 DPLL 基准失效(例如由于缺少基准或器件测量到意外频率)、则器件会进入保持模式。

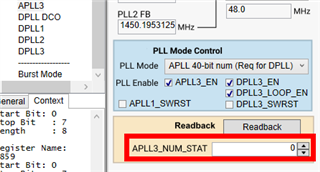

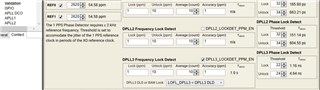

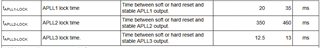

可以将输出锁相到输入、但器件仍报告 LOPL=1。 当 LOPL 阈值较低时、会发生这种情况。 例如、如果锁定 LOPL 阈值设置为1ppm、则 LOPL 状态信号将不会清除、直到 DPLL 输入和 VCO 输出之间的误差小于1ppm。 当 DPLL 处于运行状态时、DPLL 会持续更新 APLL 分子、直到输入和输出之间达到接近0ppm 的误差。

如前所述、该器件提供 ZDM 确定性的 输入到输出相位关系意味着相位误差始终已知、即使在断电/软件复位后也是如此。 确定此类确定性误差后、可以应用 DPLL 相位偏移(通过寄存器设置)来消除输入和输出之间的相位误差。 如果 DPLL 已锁定、但输入有相位变化、那么输出也会获得相位变化、从而输出保持与输入的相位对齐。 这有道理吗?

此致、

Jennifer

Jennifer、您好!

新年快乐

您的回答很合理、因此我想了解以下几点:

1.我可以将抖动清除器设置 为忽略输入时钟相位变化(输出将不会跟踪输入时钟相位)、而仅跟踪输入频率吗?

2.正如您写的"DPLL 会持续更新 APLL 分子、直到输入和输出之间达到接近0ppm 的误差。" 我是否能够不断地读取该值?

我还可以读取 输入时钟与 DPLL 测量之间的相位差吗?

3.我没有在编程指南中找到设置 LOPL 阈值的位置,您可以指向相关的 reg 吗?

此致、

HAIM

嗨、Haim:

此致、

Jennifer

嗨、Haim:

此致、

Jennifer