主题中讨论的其他器件: LMK1C1102

工具与软件:

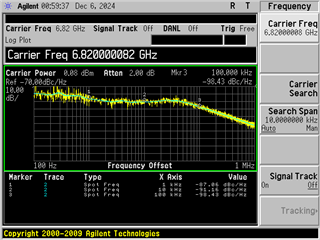

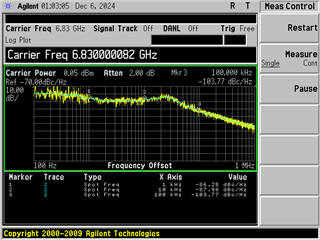

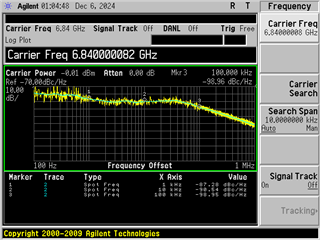

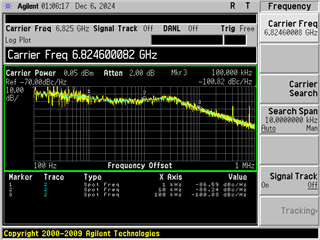

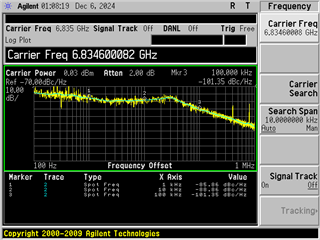

我正在将10MHz 输入参考用于 LMX2615EVM-CVAL 板。 我生成了大约6.84GHz 的输出频率并观察到输出相位噪声。 我主要关心的是100Hz-1KHz 左右的相位噪声

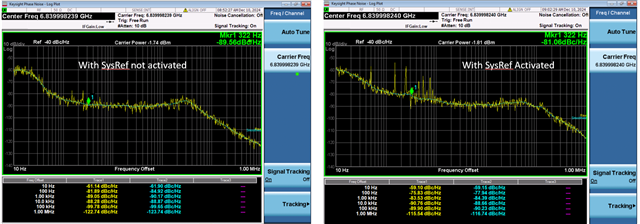

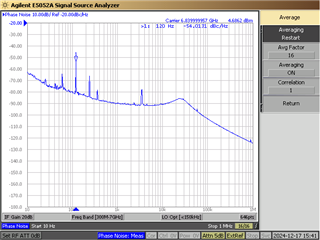

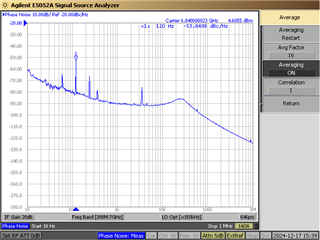

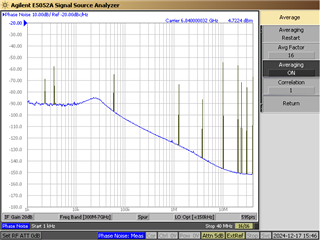

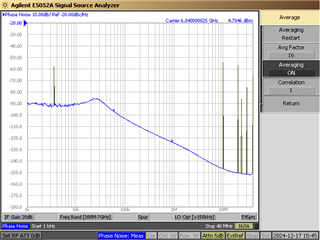

我可以观察到、即使附近是整数输出频率(即6.82GHz、6.83GHz 和6.84GHz)、相位噪声图也有很大差异(图随附)。 此外、分数 输出频率的相位噪声往往优于整数输出频率、即6.8246GHz 和6.8346GHz (附加了图)。

为什么小数输出频率的相位噪声优于整数输出频率?

为什么尽管乘法器整数的变化不大、但附近整数频率的相位噪声变化很大?

即使是最佳的相位噪声图也与 LMX2615的相位噪声规格相差甚远。 是因为我们使用10MHz 输入基准并且根据100MHz 调整了 LMX2615EVM-CAL 板吗? 调优环路滤波器是否有助于改善相位噪声? 使用10MHz 输入基准改进相位噪声有哪些选项?

此致

Deepak