Other Parts Discussed in Thread: LMK05028

工具与软件:

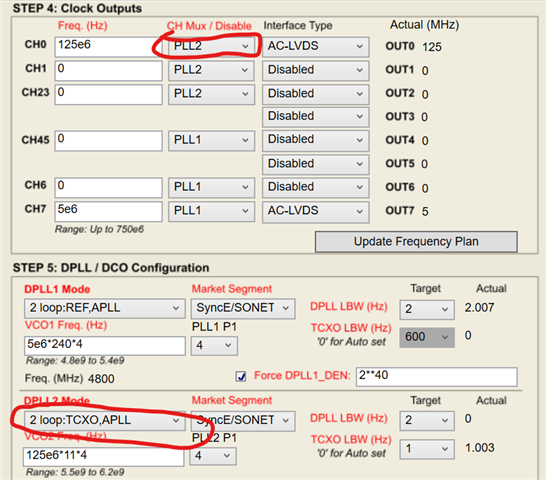

在电路上安装了"LMK05028"和下面提到的振荡器(XO、TCXO)。 REF_IN1由5MHz (LVCMOS)供电。 我们需要将125MHz (Out0)与 REF_IN1同步。

使用不同的阈值和 LBW 值进行了多项测试、然后我们将(5MHz) Out7环回 REF_IN1、但 DPLL1/2未锁定。

测试条件:

TICS 文件:

LMK05028_SyncE.TCS

XO 振荡器: 48MHz ±50ppm (ECS-3225MV-480-BN)

TCXO 振荡器: 19.2MHz ±1ppm (525L19210IT)

使用"LMK05028_SyncE.TCS"对电路板进行编程、XO،TCXO 和 REF_IN1不会出现故障。

读取寄存器 0x0D = 0x00 (XO 和 TCXO 已验证)

读取寄存器 0x2E6 = 0x20 (REF_IN1已验证)

REF_IN1监控器屏蔽寄存器如下所示:

写入寄存器 0xBE = 0x2F

尽管 APLL 被锁定、但 DPLL1/2频率和相位未被锁定。

读取寄存器 0x0D = 0x00 (APLL 1/2锁定)

读取寄存器 0x0E = 0xC0 (DPLL 1未锁定)

读取寄存器 0x0F = 0xC0 (DPLL 2未锁定)

My Schematic:e2e.ti.com/.../LMK05028_5F00_SyncE.TCS