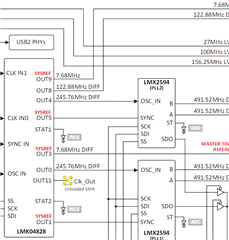

主题中讨论的其他器件:LMK04828、 USB2ANY、

工具与软件:

大家好、团队成员:

您能不能在下面帮助我们的客户查询。

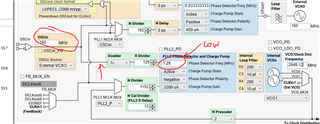

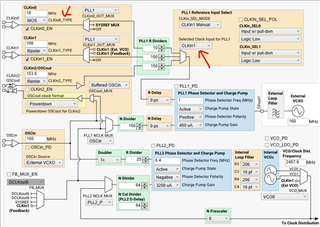

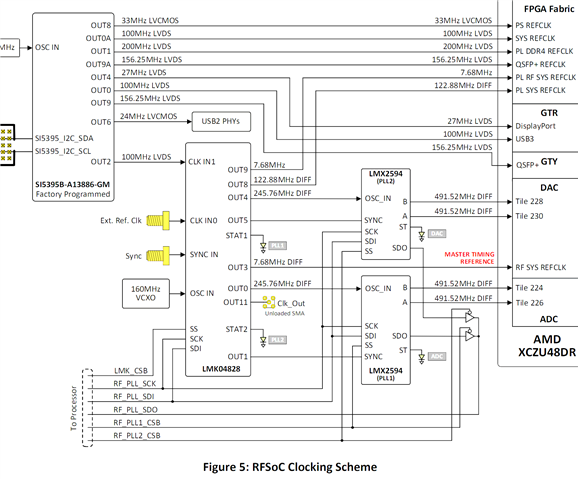

我们尝试启用 CLK_IN_0 (图1)以使10MHz 信号与器件同步。 请查看 TICS 和 PYNQ 论坛

https://discuss.pynq.io/t/xrfclk-configuration-lmk04828-using-external-10mhz-reference-clock/5562/12

https://e2e.ti.com/support/clock-timing-group/clock-and-timing/f/clock-timing-forum/1229913/lmk04828-taking-driving_clock-from-another-input-pin-and-i-can-t-figure-out-which-one/4661353#4661353

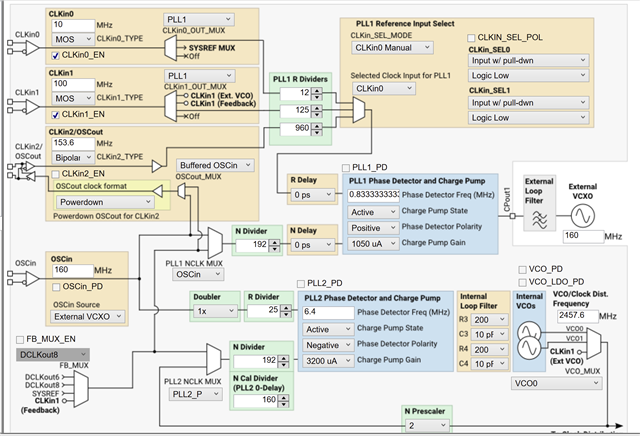

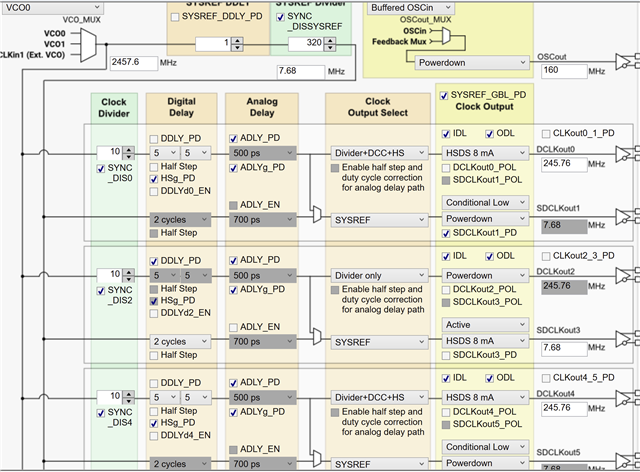

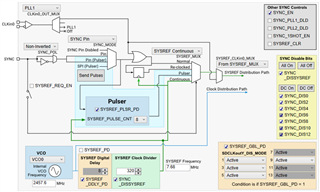

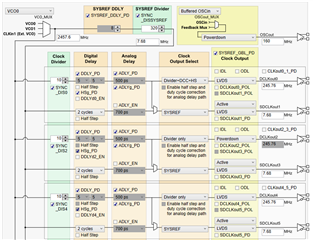

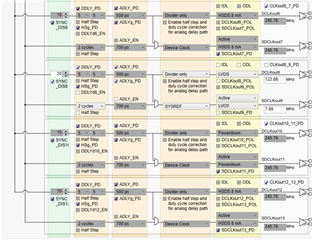

我遇到了3种不同的解决方案。 提供了用于为每个导入十六进制的.txt 文件。 使用 TICS PRO、我要将我们的电路板配置为具有10MHz 外部时钟控制、同时禁用 OSCin 内部参考时钟。 图像上的其他频率应保持不变。 我不想通过使用 USB2ANY 电缆以及其中的任一.txt 文件来对电路板进行十六进制导入编程、因为我们没有 RFSoC4x2的默认 LMK04828 .tcs 文件。 您能给我们提供一些帮助吗? 我们真的很困倦、Real Digital 不为我们提供电路板的默认 LMK04828文件。

此致、

Danilo.