主题中讨论的其他器件: LMX2571

工具与软件:

你好

我们在无线电模块中使用 LMX2572LP。

这可以在高达500mW 的传输功率下正常运行。

但是、我们想创建一个6瓦射频功率的概念、但是

这些杂散对于这一点非常强大。 我们必须符合-54 dBm 干扰标准

的组件级别。 我们对其期待的是能够生产出类似芯片的产品

杂散显著减少。

140 MHz 上的 RF 载波在这里用一个陷波滤波器进行抑制。

此致

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

你好

我们在无线电模块中使用 LMX2572LP。

这可以在高达500mW 的传输功率下正常运行。

但是、我们想创建一个6瓦射频功率的概念、但是

这些杂散对于这一点非常强大。 我们必须符合-54 dBm 干扰标准

的组件级别。 我们对其期待的是能够生产出类似芯片的产品

杂散显著减少。

140 MHz 上的 RF 载波在这里用一个陷波滤波器进行抑制。

此致

Noel、您好

我无法回答您的问题、因为开发是由外部开发人员完成的。 他说他不能再做了。

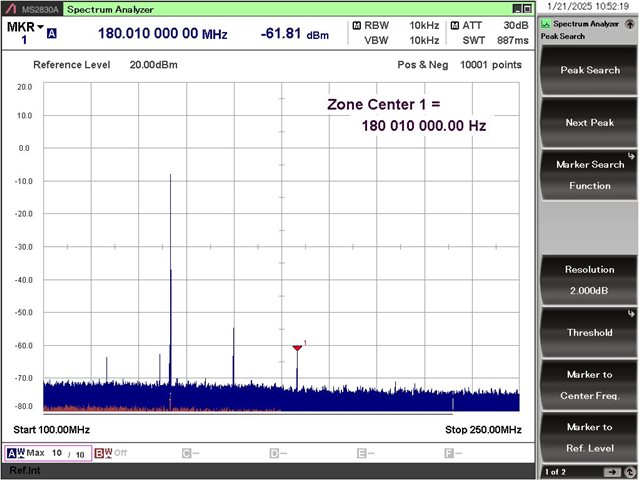

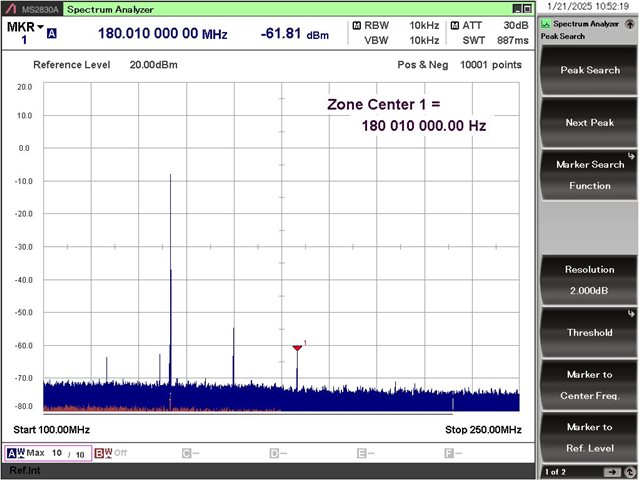

这里我有一个从我们使用评估板进行的开发开始的频谱。

这似乎向我们显示了芯片的正常杂散行为。

或者是否有更好的方法、我们做了一些错误的事情?

杂散为-80/-90dBm。 对于6瓦、我们必须使用以下的功率

40 dB 放大、因此-90 dBm 变为-50 dBm、这对于 EN300113来说太大了。

这就是我们认为可能有一个杂散行为更好的类似芯片的原因。 此类芯片的典型特征是什么?

此致

Noel、您好

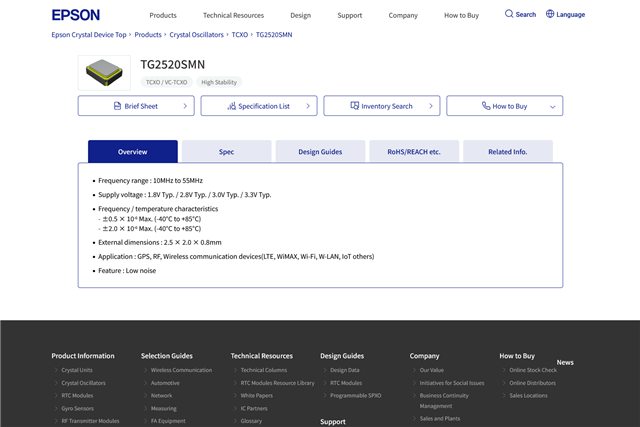

对于射频模块、我们使用具有50 MHz 振荡器频率的 TG2520SMN。 这个数字是 LMX 2572 LP 中的100 MHz 的两倍。

https://www.epsondevice.com/crystal/en/products/crystal-oscillator/tg2520smn.html

这可以测量图1中的频谱。

图2是使用评估套件的原始100 MHz 振荡器测量的。

我们还对电路板和评估套件进行了比较测量、找不到两者之间的任何主要差异。

这就是为什么出现这些杂散是这种技术的一个根本问题、是不可避免的想法。 问问自己、到底有没有更好、更差的芯片、可能取决于功耗。

如果欧盟所有频率的干扰发射限值均为-36dBm、但遗憾的是、我们必须在宽频率范围内符合-54dBm 的要求、那么上述任何一个问题都不会是大问题。

如果这些杂散是基本技术问题、我们需要为6瓦项目找到另一种解决方案。

此致

D.W.

嗨、Dirk、

我相信您的应用有很多频率通道、如果您的规格需要优于-90dBm 的杂散、我认为合成器(具有集成 VCO 的 PLL)可能不是一个好的解决方案、因为芯片内的串扰是不可避免的。 与本例中的20MHz 杂散一样、环路滤波器应该会将其滤除、但我看到 EVM 中的杂散为-75dBm。 此水平的杂散并不差、但仍然距离目标较远。 这很可能是由于串扰所致、我们无法通过外部方法加以改进。

我想您需要分立式解决方案、即 PLL + VCO、来满足杂散要求。

嗨、Dirk、

串扰可能发生在芯片内部以及输入和输出之间;输入和 VCO 等 这是因为芯片尺寸小、但集成了所有元件、因此分立式解决方案可避免串扰。

为什么需要 div/2? 您的 VCO 300MHz 是吗?

LMX2571支持外部 VCO 并允许使用内部分频器和输出缓冲器。 如果您有一个可处理脉冲整形和过采样的强大处理器、则该器件还支持 FSK 调制。

https://www.ti.com/product/LMX2571