主题中讨论的其他器件: LMK1D1204

工具与软件:

您好!

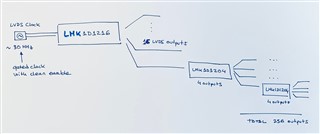

我正在研究仪表机箱的时钟分配树。 我先描述一下主要模块、

1) 1)具有干净输出使能功能的精密 LVDS 时钟振荡器(允许打开和关闭无干扰的开关)。 该频率 在30 MHz 附近。

2) LMK1D1216、用于制作 输入时钟的16个副本。

3) 3) LMK1D1204器件的两个级联电平。

简而言之、该树生成256个主输入时钟副本。 请参阅随附的 sketch。

现在、问题来了。 我们要求 、当将主时钟振荡器从关闭状态切换到导通状态时、启用的时钟的第一个边沿 以 较小的偏斜到达所有256个输出。 我们可以承受1000ps 的最大偏斜、因为我们将随后校准输出之间的偏斜、

-您能确认 LMK1D12xx 设备 没有存储器吗? 我们已丢弃了其他时钟缓冲器、其中包括某种用于检测传入时钟是否存在的数字滤波器、因此在启用输入时钟后、会在输出中引入可变的1、2或3周期延迟。 对于这些其他器件、在开始时会滤除一些时钟周期。 但是、接收器(分配树末端的仪器)需要接收所有传入的时钟脉冲并进行计数、256个仪器中的每个仪器都有一个必须全局同步的时间计数器。

-要 估算 256个输出之间的偏斜,如果我对 LMK1D1216 (不同输出之间)和 LMK1D1204的两层(这会导致相邻的部件间偏斜和相同部件输出偏斜)引入的偏斜进行正交求和,是否可以?

感谢您的帮助!

Jose Jimenez