工具与软件:

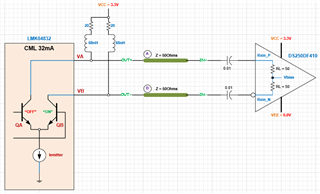

我正在双环路模式中使用 LMK04832。

1. PLL1参考是100MHz

2. PLL2基准为156.25MHz 外部 VCXO [馈入 OSCin]

3. PLL1 R = 16、PLL1 N = 25

4.目标是运行 PLL2的内部 VCO [VCO1]@ 1.611328125GHz

5. PLL2 R=8、PLL2 Pre-N=5、PLL2 N=33

我想将{2}输出时钟配置为 CML 32mA。

问题1: 这些以1.611328125GHz 频率运行且配置为 CML 32mA 的输出时钟是否来自"偶数"时钟输出引脚或"奇数"时钟输出引脚?

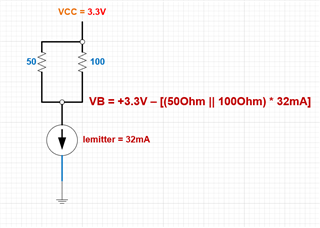

A)。 直流端接分析

VOD = 1660mV [端接50Ohm 上拉至 Vcc]

当 QB ="关闭"时、QA ="打开"

- VA =+3.3V

- 32mA 流经50Ohm 电阻器[外部 Rb]设置 VB = 3.3V -[(50Ohm)*(32mA)]= 3.3V - 1.6V = 1.7V

当 QB ="开"时、QA ="关"

- Vb =+3.3V

- 32mA 流经50Ohm 电阻器[外部 Ra]设置 VA = 3.3V -[(50Ohm)*(32mA)]= 3.3V - 1.6V = 1.7V

VOD = 1.6V [数据表显示为1600mV];我是 很好 在此计算中!

2. Vod = 1070mV [端接50 Ω 上拉至 Vcc、在负载侧与100 Ω 端接进行交流耦合]

当 QB ="关闭"时、QA ="打开"

- VA =+3.3V

- 32mA 以"并联"方式流经50 Ω 电阻器[外部 Rb]、负载[负载= 100 Ω]设置 VB = 3.3V -[(50 Ω|| 100 Ω)*(32mA)]= 2.233V

当 QB ="开"时、QA ="关"

- Vb =+3.3V

- 32mA 以"并联"方式流经50 Ω 电阻器[外部 Ra]、负载[负载= 100 Ω]设置 VB = 3.3V -[(50 Ω|| 100 Ω)*(32mA)]= 2.233V

VOD = 1.0667V [数据表显示1070mV];我是 很好 在此计算中!

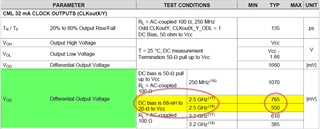

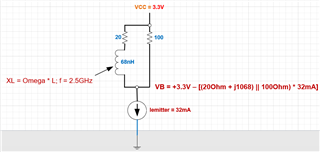

B)。 交流端接分析

VOD = 550mV 至765mV [直流偏置为68nH 至20Ohm 至 Vcc、在负载侧具有100 Ω 终端的交流耦合]

Z{电感器}@ 0GHz = j * Omega * L = j * 2 * Pi * 0GHz * 68nH = J0欧姆[@ d.c.]

Z{电感器}@ 2.5GHz = j * Omega * L = j * 2 * Pi * 2.5GHz * 68nH = j1068欧姆[@ 2.5GHz]

当 QB ="关闭"时、QA ="打开"

- VA =+3.3V

- 32mA 流经与负载[100 Ω]并联的20 Ω+ 68nH 电感器、 设置 VB = 3.3V -[(20 Ω+ J1068)|| 100 Ω)*(32mA)]

我一定是造成某种数学误差、因为当我尝试求解这个方程时、我没有得到 VOD = 765mV [IDL = 1]或 VOD = 550mV [ODL = 1]

问题2: 您能否概述数学步骤以获得 VB = 3.3V -[(20Ohm + j1068)|| 100Ohm]* 32mA = 2.535V [VOD = 765mV]或 VB = 3.3V -[(20Ohm + j1068)|| 100Ohm]* 32mA = 2.75V [VOD = 550mV]?