Other Parts Discussed in Thread: LMX1204, LMX1204EVM

工具与软件:

尊敬的专家:

我的客户正在评估 LMX1204、有疑问。

如果您能提供建议、我将不胜感激。

——问题

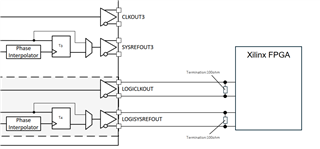

如附加配置所示、LMX1204的 LOGICLKOUT 连接到 FPGA。

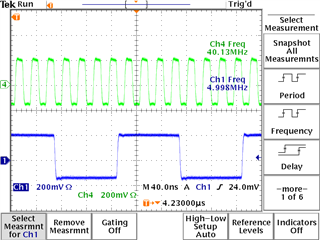

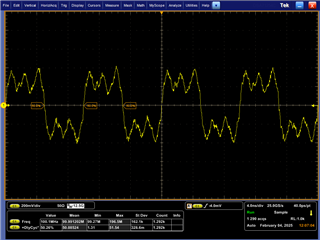

观察 FPGA 端的 LOGICLKOUT 波形时、会观察到大的振铃。

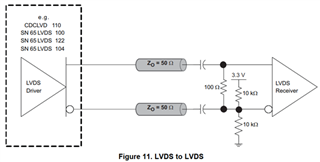

-将 LOGICLKOUT 和 LOGISYSREFOUT 的输出格式设置为 LVDS。

-通过直流耦合连接到 FPGA (直接连接)。

-在100Ω 端(接收端)安装一个 FPGA 端接电阻器。

观察 FPGA 末端的 LOGICLKOUT 波形时、会发生如下所示的振铃。

问题1:

根据 LMX1204EVM 用户指南中的电路图

输出通过交流耦合(0.1uF)输出到 SMA 连接器。

LVDS 输出是否需要交流耦合?

※这是否意味着不能使用直流耦合?

问题2:

如果可以进行直流耦合、仅在接收侧使用100 Ω 终端(如所附图所示)是否足够?

问题3:

据我了解、与 LVDS 输出相关的唯一寄存器设置是输出格式和 Vcm 设置。

是否有任何其他设置需要设置?

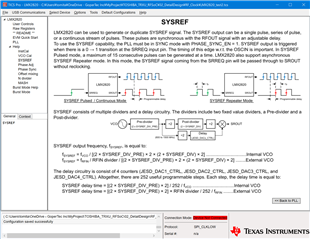

我已将配置文件附加到此电子邮件中、因此如果设置中有任何错误、如果您能告诉我、我将不胜感激。

问题4:

如果配置、连接或设置没有问题、您认为引起严重振铃的原因是什么(如附图所示)?

不过、当我修改此配置以使用 LVPECL (交流耦合)时、没有发生振铃、时钟波形也很好、因此我认为印刷电路板上的布线模式不存在问题。

ーーー μ A

感谢您提前提供的大力帮助。

此致、

Shinichi