Other Parts Discussed in Thread: ADC16DV160

工具与软件:

尊敬的团队:

我们在设计中采用的 ADC 器件(ADC16DV160)为 Fin=ADC 70MHz、 采样频率160MHz。

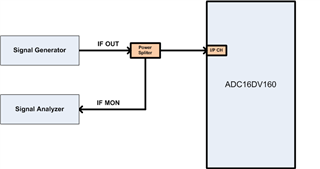

我们已根据图像通过功率分频器将信号发生器的 Fin 连接到 ADC16DV160 ADC 和频谱分析仪。

在这种情况下、根据附加的图像、我们的频谱中存在一些杂散。

观察到的杂散频率:FS + Fin = 230MHz、Fs-Fin = 90MHz、2FS+Fin = 390MHz & 2FS-Fin = 250MHz。

您能说明产生这个 杂散源的原因吗?

是否有应用手册说明过这种影响?

频谱中观察到的杂散是否会影响我的 ADC 性能?

此致、

Esakki。