Other Parts Discussed in Thread: DAC38J82EVM

工具与软件:

你好

我们 通过 FMC 连接使用 DAC38J82EVM 和 KintexUS+电路板 来创建 JESD204B 系统。 我们使用 TI 的 TI204C-IP。

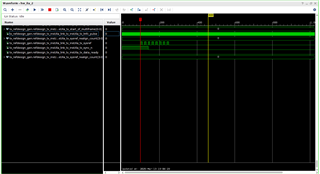

通过 DAC38J82EVM GUI 初始化 DAC 后、我们从 DAC 向 FPGA 发送 SYNC 置位。 假设 FPGA 在所有8个通道中发送所需的/K/、我们希望 DAC 根据规范的子类1操作取消 SYNC 置位。 但是、这种情况从未发生。 DAC38J82EVM GUI 也不会显示任何警报。 请参阅随附的 ILA 波形。

我们通过在 FPGA 中使用 ibert 内核来验证 SEDES、以生成各种随机测试图形、并在 DAC 端验证它们、并且运行正常。

这可能是由 sysref 信号时序问题引起的吗? 作为 FPGA 的器件时钟、我们使用来自 EVM (LMK0482x)的 clock12、而作为 FPGA 的 sysref、我们使用来自 EVM (LMK0482x)的 clock1。 它们不是来自同一组时钟发生器芯片。 我们之所以必须这样做、是因为 FMC 连接器到 FPGA 引脚的接线存在限制。

如果这不是由 sysref 问题导致的、则发生这种情况的唯一可能性可能是 TI204C-IP 不发送/K/序列。 什么原因可能导致这种情况? 我们已经 仔细检查了 IP 内核的配置和连接。

此外、我们是否有任何调试方法可以用来查看串行线的活动?

谢谢

a.