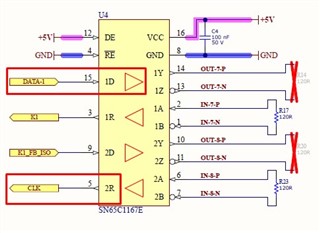

Other Parts Discussed in Thread: SN65C1167E

主题中讨论的其他器件:SN65C1167E

工具与软件:

尊敬的先生或女士:

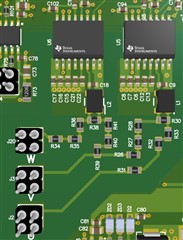

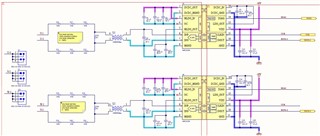

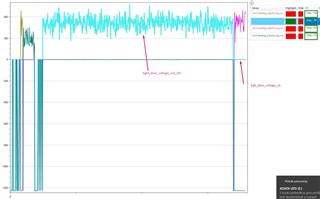

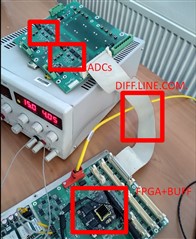

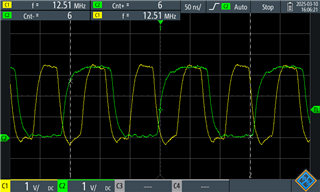

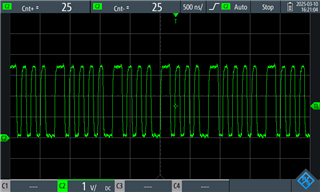

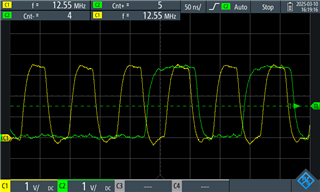

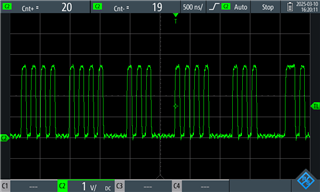

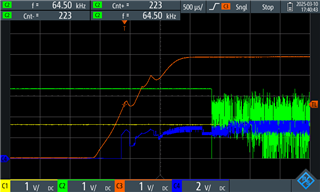

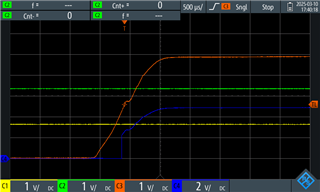

我们在使用 Δ-Σ ADC 时遇到功能问题。 我们在我们的应用中使用它来测量相位间的交流电网电压。 我们被迫降低20MHz 到12.5MHz 时钟频率的频率、但我们在12.5MHz 时的器件测量的电压具有直流失调电压(请参阅附件)。 在10Mhz 时、问题消失了。 接近12.5MHz 越多、ADC 添加一些直流失调电压后的 si 概率就越大(意味着器件应发送50%零/一、但以0V 输入发送75%或35%等) 我在12.5MHz 时获得了可能的解决方案、但我们想更多地使用这个 IC、所以我需要找到这个问题的根源。 你有什么想法可能导致这种情况吗? 直流偏移是随机常数、看起来像是调制器故障。

感谢 Thomas 硬件工程师