请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC3482 工具与软件:

您好、TI 工程师

每次打开电源或输入复位时、DAC3482输出波形中的8x 时钟杂散电平输出都会波动。

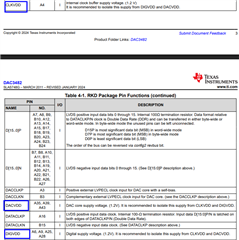

时钟是 DATACLK 端子的信号输入。

如何将8x 时钟杂散稳定到低电平?

提前感谢您。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好、Hirai-San、

请帮助确认8x 时钟意味着 FDAC/8杂散。 例如、如果 DAC 在1GSPS 下运行、则杂散将为1GHz/8 = 125MHz。

如果是、由于 FIR 设计的性质和功耗优化设计、DAC3482具有一些内部的 FS/8时钟。 我们可以尝试通过以下方法降低能量:

为了确保输出不会波动、可以确保通过确定性 OSTR (双同步源模式)初始化内部 FS/8时钟、以便内部时钟分频器确定对齐。

有关详细信息、请参阅第3节: https://www.ti.com/lit/an/slaa584/slaa584.pdf

此外、您可以看到是否可以增加 DAC3482的 DIGVDD (数字 VDD)、DACVDD (DAC 编码器逻辑)和 CLKVDD (时钟电源)之间的电源滤波

数字电源噪声将包含 Fs/8元件。 如果您可以对三个电源轨之间的电源进行额外的滤波、这将更大限度地减少 DAC 电源上的 Fs/8能量量。

谢谢你

-Kang