工具/软件:

TI-ADS1261 ADC 始终在 SPI 总线上将值为零的字节传输回主器件。

TI-ADS1261 模数转换器通过 Zynq SPI 总线串行接口连接到 Xilinx Zynq 7020 SOC (片上系统)。 用于通信的引脚包括 CS (芯片选择)、SCLK (串行时钟)、DIN (数据输入)和(DOUT/DRDY)数据输出/数据就绪。 SlCK 以33 MHz / 512 = 65.104KHz 运行、周期为15.36微秒。

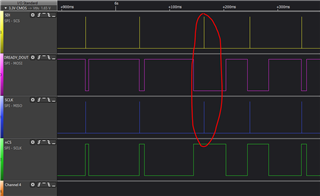

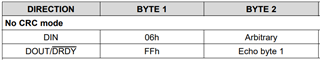

ADS1261为了响应命令和读取寄存器传输正确数量的字节数、但所有字节的值均为零。 例如发送复位命令- 0x06、0x00,1261以0x00、0x00而不是0xFF、0x06进行响应。 或发送状态寄存器= 0x21、0x00 1261的 RREG、以 0x00、0x00、 0x00而不是0xFF、0x21做出响应 。

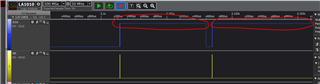

我的硬件工程师在 SCLK、DIN 和 DOUT 上放置了一个示波器。 时钟看起来正常、DIN 由 Zynq SPI 正确驱动、DOUT 由1261驱动、每个字节都具有串行零的字节。

我们的软件正在进行如下初始化。

复位 SPI、首先初始化 SPI 总线系统时钟、中断、配置寄存器、 复位 SPI。 如下所示:

Xilinx SPI 配置寄存器 CR = 0x0000FC35

//位17 = 0模式失败生成禁用

//位16 = 0手动启动命令

//位15 = 1手动启动使能

//位14 = 1手动片选模式

//位13:10 = 1111未选择从器件

//位9 = 0外设选择仅解码1 0f 3选择

//位8 = 0使用 SPI 基准时钟

//位7:6 = 0保留

//位5:3 = 110波特率除数除以128

//位2 = 1时钟相位 SPI 时钟在字之外无效

//位1 = 0 SPI 字之外的时钟极性 SPI 时钟为静态低电平

//位0 = 1模式选择 SPI 处于主模式

然后、我们使用初始化的 SPI 总线来初始化 TI-ADS-1261、如下所示:

发送命令复位、读取状态寄存器、使用默认值写入所有寄存器。

TI-ADS-1261对复位 命令和所有写入寄存器命令均为全零作出响应。

我们使用 TI-ADS-1261作为我们的 ADC、用于从我们的硬件实时读取各种关键电压。

非常感谢您为帮助让 TI-ADS-1261正常运行所提供的帮助。