主题: AM5728中讨论的其他器件

工具/软件:

使用相同的寄存器设置、只是将 DCLKIN 频率从12MHz 更改为40.96MHz 会导致读取的数据从大约11000的计数更改为大约12000的计数。 我们会馈送直流电压以进行测试。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

使用相同的寄存器设置、只是将 DCLKIN 频率从12MHz 更改为40.96MHz 会导致读取的数据从大约11000的计数更改为大约12000的计数。 我们会馈送直流电压以进行测试。

这是适用于12MHz 输入的寄存器设置。 它们在启动时按顺序写入一个 for 循环。

//低16位是寄存器/值的组合、例如寄存器0x7的值为0x6C

您好、Tom、

确保我正确理解您的问题:您在16倍实时抽取率模式下使用 ADC3660 (您已确定在此模式下、采样 CLK 和 DCLK 具有相同的频率)。 您首先在12MHz 处使用样片 CLK 和 DCLK 进行了测试、并获得预期的数据样本数。 然后、您将 Sample CLK 和 DCLK 更改为40.96MHz 并获得意外数量的样本?

还有一些问题:

此致、

Luke Allen

您好、Tom、

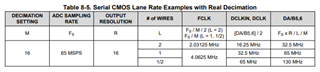

我可以看到、因此当您对直流电压进行采样并更改 DCLK 频率时、ADC 代码会发生变化。 需要注意两点:正如 Rob 提到的、DCLK 取决于示例 CLK、因此您必须同时更改两者。 此外、当 ADC3660处于16位、1线、实际抽取/16模式时、DCLK 为0.5 *样本 CLK、它们不相同。 这可能会导致数据被错误读取。 可以使用数据表中的以下公式计算 DCLK 频率(仅适用于旁路或实际抽取):

DCLK 频率=(采样 CLK 频率*分辨率/电线数量/抽取因子)/ 2

此致、

Luke Allen

您好、Tom、

我无法评论为什么当提供了不正确的 DCLK 频率时数据似乎正确。 如果您希望器件按照数据表中记录的那样运行、我建议使用数据表中记录的器件。 计算旁路/实际决策模式下所需 DCLK 频率的公式可在数据表的表8-5中找到。

由于您在 FS = 40.96 MHz 时使用16位、单线、16倍实时抽取率模式、因此 DCLk 频率应如下所示:

DCLK 频率=(40.96M * 16 / 1 / 16)/ 2

DCLK 频率= 20.48 MHz

请 确保正确无误。 我还在实验室中测试了 ADC3660、并使其在您的模式下运行。 我已为您的模式附加了正确的配置。 请注意、此配置取决于序列、因此寄存器必须按相同的顺序进行编程、才能正确配置器件。

e2e.ti.com/.../ADC3660_5F00_16Bit_5F00_1W_5F00_RealDec16.txt

此致、

Luke Allen

您好:

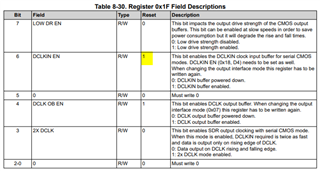

您可以更正、在我提供的上述配置中、不会写入这些寄存器。 这是因为默认启用 DCLKIN 缓冲器、这意味着0x18位4和0x1F 位6默认设置为1。 在1W、实时抽取模式下、输出数据被串行化、并且必须启用 DCLKIN 缓冲器。

如果您对您的应用有任何与配置相关的其他详细信息、请告诉我、我可以帮助您获得工作配置。 如果需要、请告诉我、我们可以将讨论移至电子邮件。

此致、

Luke Allen