工具/软件:

此问题的原始线程已关闭、但未解决。

最初的问题是、TI-ADS1261在 DOUT 线路上不会对 Xilinx Zynq 7020 SPI 总线在 DIN 上发送给它的命令做出响应。 1261对复位命令的响应不一致、复位命令通常在 DOUT 上静音失败、然后在大约四十次尝试后、1261开始响应复位0x06、0xFF 和 DOUT 0xFF、0x06。 但一旦1261得到使用相同总线和相同软件的 RREG 命令,它就会完全停止响应。

目前、我有许多单独的命令连续运行、包括 NOP、RESET、LOCK、UNLOCK 等多项测试。

但是、只要我尝试执行 RREG 命令、一条 RREG 命令就会成功、那么所有响应都将从1261停止、包括之前有效的 RESET。 无论进行多少次复位、在 RREG 之后都是如此。 使1261在 RREG 之后再次工作的唯一方法是下电上电。

我注意到、我需要以某种方式修复的另一个问题是、上电后、1261开始响应之前、需要发送25到100条复位命令。 对于任何命令、我都不会做任何不同的事情。

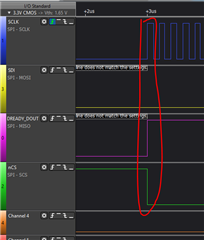

下面的第一个图显示了一系列尖峰、这些尖峰都是具有响应的良好复位命令、并被软件报告为成功。 第二个图显示了时钟电平上第一个复位尖峰的时钟电平视图。 第三个显示了 RREG 命令之后复位的时钟电平视图、这是1261在 RREG 命令之后停止响应后的数百个之一。

从第二个图中可以看到、我的时钟设置现在看起来非常好。 总线时钟在发送和接收期间开启、之后变为低电平。 从图中可以清楚地看出、DIN 在1261时钟上升沿锁存、因此它在下降沿提供稳定的读取、而1261 DOUT 看起来像在时钟下降沿锁存、正如我想您在上面提到的那样。

这次我还包括我的完整软件日志文件。 此文件中没有任何专有内容。 日志文件显示大约40个 reset 命令失败、直到它在第454行开始工作、然后八次成功重置。 然后切换到命令、第一个 RREG 命令在第483行成功执行。 之后1261没有响应任何东西。 请记住、我的软件对于通过和失败复位以及 RREG 完全相同。

我需要帮助了解1261会延迟对 RESET 的响应的原因、以及它在收到 RREG 命令后停止响应的原因?