Other Parts Discussed in Thread: AFE2256

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AFE2256 工具/软件:

您好:

我需要澄清 第7.1.2节:从 AFE2256 ROIC 数据表的 AFE2256生成栅极驱动器信号。

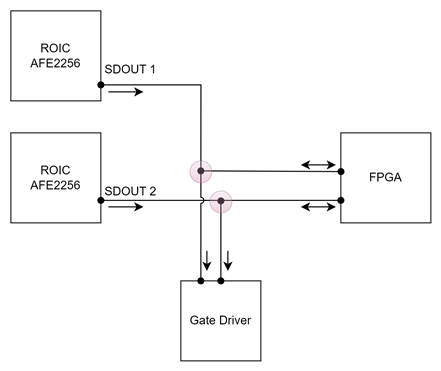

首先、关于 SDOUT 信号、数据表是否建议 ROIC、FPGA 和栅极驱动器之间的以下电气连接?

如果正确、我认为在使 ROIC 与 SDOUT 引脚上的 FPGA 通信时、需要考虑 ROIC/FPGA 和栅极驱动器结之间的隔离。

您对此有何看法?

关于 AFE2256发送的探头栅极驱动信号(PROBLE_SIGNAL 字段值(寄存器5Ah)、40h)、我认为它 仅是上升沿和下降沿。

我知道这个上升沿和下降沿要由 FPGA 用于触发 在同一行上 从 FPGA 到栅极驱动器的信号、例如:开始线路扫描、发送时钟信号或其他信号

这是它的工作方式吗?

感谢您对此的意见!