主题: ADS127L11中讨论的其他器件

工具/软件:

数据表指出、标称 CLK 和 SCLK 输入电压为0.6V、但未指定允许的最小值或最大值。 如果微控制器偏离了正常配置、并向时钟引脚施加 CLK/逻辑高电平、而不是向~0.6V 振幅的时钟信号施加 CLK/逻辑高电平、是否会对 VCC 或 SCLK 引脚造成损坏?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

数据表指出、标称 CLK 和 SCLK 输入电压为0.6V、但未指定允许的最小值或最大值。 如果微控制器偏离了正常配置、并向时钟引脚施加 CLK/逻辑高电平、而不是向~0.6V 振幅的时钟信号施加 CLK/逻辑高电平、是否会对 VCC 或 SCLK 引脚造成损坏?

尊敬的 Elias Tarver:

您之所以使用 ADS1251 (自2001年起)而不是较新的 ADC、有什么原因? 例如、ADS127L11在几年前发布、与 ADS1251相比、它在各种可能的性能和功能指标方面都更出色、价格也相似。 或者、如果您能详细分享您尝试测量的内容、或许我们可以为您提供一款集成度更高的器件。

如果您最终决定使用 ADS1251、当然可以回答您的问题、我只想确保 您了解所有选项

-布莱恩

尊敬的 Elias Tarver:

我懂了。

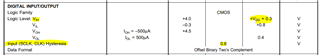

我可以在 ADS1251数据表中找到的与 SCLK/CLK 相关的0.6V 规格是关于迟滞的规格。 请参阅下图。 这是您所指的吗?

请注意、在这些引脚上施加的最大电压由 V_IH 给出、可高达电源电压(VDD)。 此外、还应注意、最大 V_IL 为0.8V、因此施加0.6V 振幅时钟信号就像对 ADC 的恒定0一样

-布莱恩