工具/软件:

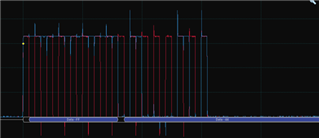

我在读取 ADS1261到 ESP32S3的最终 DOUT 位时遇到问题、它始终恢复到低电平。 使用 PicoScope 示波器:

可以看到、在 SCLK 的最后一个下降沿(红色)之后、DOUT (蓝色)立即变为低电平。

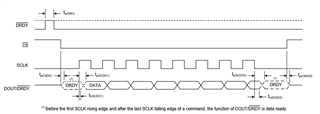

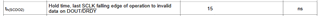

通过查看数据表、我们可以看到在最终下降时钟沿后 DOUT 保持的有效时间为 th (SCDO2)

th (SCDO2)的最小值为15ns、因此我们必须考虑这种可能性。

使用 Espressif IDF 框架时、我无法确定何时读取精确的数据、但根据 ADS1261数据表、我已将其设置为 SPI 模式1。

现在、我找到了一种权变措施。 通过将 SPI 时钟频率设置为50MHz、从时钟下降沿到下一个上升沿的时间为10ns。

这将强制 ESP "更快地读取比特"。 这意味着 ESP32S3在最短15ns 时间内读取数据。

但是、再次查看数据表、规定的最小 SCLK 周期为97ns。 使用50MHz 时、SCLK 周期为20ns。

尽管如此,它仍然有效,我还没有看到任何中断的沟通。 但是、我想在规定的时间要求范围内操作。

我想澄清一下我的想法是正确的。 似乎很奇怪的是、该芯片允许低至1kHz 的 SPI 通信、但在最后一个下降沿会强制您在15ns 内读取该位、或存在不正确的数据风险。