Other Parts Discussed in Thread: DAC8742H, TIDA-01504, DAC8742HEVM

主题中讨论的其他器件: TIDA-01504、

工具/软件:

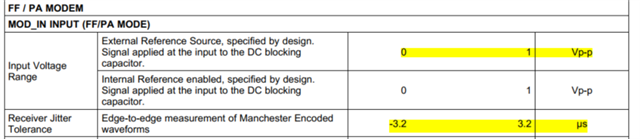

我将使用 DAC8742H 开发现场总线应用。 变送器驱动器板取自 DAC8742H 数据表。 但是、当我完成物理层测试时、在接收抖动容差测试中失败。 我认为问题出在 DAC8742H 本身、因为 BUS+直接连接到 DAC8742H 的 MOD_IN (通过直流移除电容器)。 我查看了 DAC8742H 数据表、发现抖动容差为+-3.2us

然而、当将我的参考发送器的抖动设置为3.2us 时、DAC8742H 每1000条发送的消息仅获得95-97%的抖动。

我的问题是:

- 数据表中所述的3.2us 抖动容差是否有任何"安全裕度"? 例如、如果抖动为3.21us、我们正确收到消息的可能性/百分比是多少?

- DAC8742H 或任何相关的设计(如 TIDA-01504)是否通过了物理层测试?