Other Parts Discussed in Thread: ADS1271

工具/软件:

您好、

在高速模式下使用 ADS1271的 Im、SPI SCLK 频率为 27MHz、同时 ADC 的时钟频率为27MHz。

当 SYNC 引脚被拉高时、以使 DRDY 在10usec 后。

但一旦我开始 SPI 通信、DRDY 就会保持低电平 的时间更短、并在 DRDY 为高电平时获取 ADC 采样数据

DRDY -黄色 DOUT -蓝色

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 Priti、

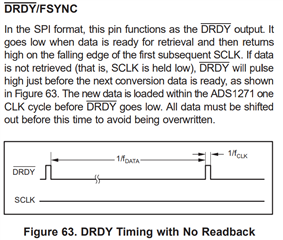

这是正常行为。 在高速模式下、fCLK=DRDY 27MHz、/DRDY 下降沿之间的时间将为9.48us。 该时间不会改变、但/DRDY 保持高电平的时间量取决于您是否正在读取数据。

在/DRDY 下降沿之后读取数据时、/DRDY 引脚将在 SCLK 的下一个下降沿变为高电平、并保持高电平、直到下一个转换数据就绪。 但是、如果您没有读取任何数据、则没有 SCLK 下降沿来再次强制/DRDY 为高电平。 在这种情况下、/DRDY 将保持低电平、直到下一个转换数据就绪之前的1个 CLK 周期、并在1个时钟周期内变为高电平、然后再次变为低电平。

有关更多详细信息、请参阅图69和/DRDY 部分:

此致、

Keith Nicholas

精密 ADC 应用