工具/软件:

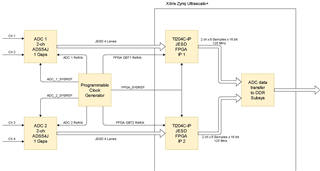

我们并行使用两个 TI204C-IP JESD FPGA IP 从两个 ADC 接收同步数据、如下所示:

我们遵循以下建议(来自 TI204C-IP JESD FPGA IP 用户指南)实现两个 JESD IP 之间的同步:

- 仅在设置了两个 JESD IP 的"rx_all_lanes_locked"后、才将"rx_release_all_lanes"输入设置为"1"。

- 为多个 ADC 和多个 FPGA Rx IP 实现确定性延迟、即将裕度值为2-5个周期的"cfg_rx_buffer_release_delay"调优为在"rx_lmfc_to_buffer_release_delay"输出上检测到的最坏情况延迟数。

- 在 FPGA 输入端的 SYSREF 和 JESD IP 之间添加几个触发器;

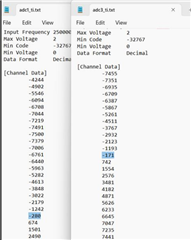

在大多数情况下、当不同 ADC 之间的所有数据都发生最小的移位(1个样本或更少)时、我们可以获得良好的结果。 但有时、在下电上电后、我们会增加两个不同 ADC 的通道之间的相移、这始终是8个差分 ADC 样本。 这不会在单个 ADC 上的通道之间发生、仅在不同 ADC (例如通道1和3、或2和3)之间以及不同 JESD IP 之间发生。

您能否就导致此类行为的原因以及如何解决此类行为提供一些额外建议?

谢谢、

Ryan