请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:DAC8562 工具/软件:

尊敬的 TI 支持团队:

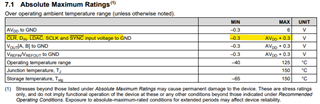

我已使用3.3V 电源和一个单独的一个 (3.3V 数字)上拉电源将 AVDD 连接到所有数字输入 CLR、DIN、LDAC、SCLK 和 SYNC。

我想分析仅启用上拉电压而不启用 AVDD 的情况。 我观察到上拉电阻器上的压降会在 AVDD 未开启时减小引脚电压。 这是因为 IC 内部电路连接导致有灌电流。 这是否会导致可靠性问题并损坏 IC?

我确实需要评估这一点、因为两个电源都来自另一个外部电路板、在某些情况下可能都未同时通电。