工具/软件:

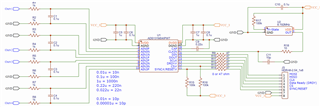

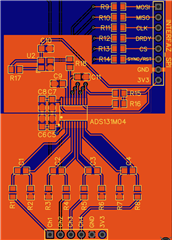

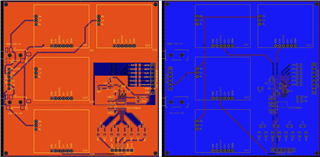

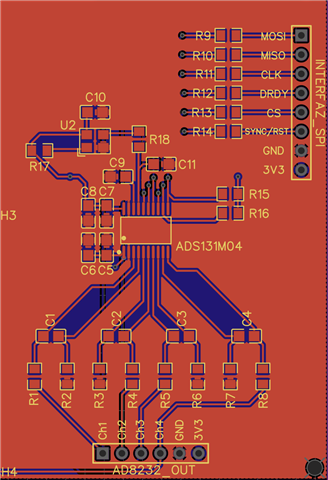

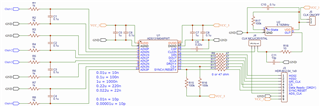

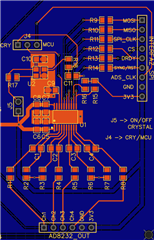

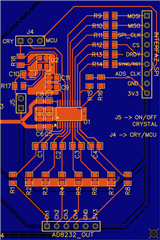

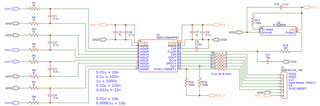

我试图用一些 Arduino 代码测试它,我在 GitHub 上发现,据称是工作的。 因此、我假设编程不是问题。 那么、我想问我的设计是否正确。 我是根据数据表中的信息和我在网上找到的其他设计构建的、但无法正常工作。

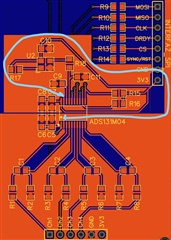

您能告诉我设计是否正确吗?

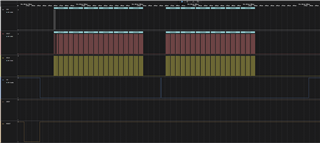

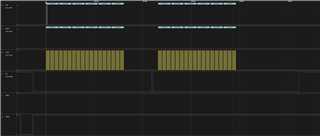

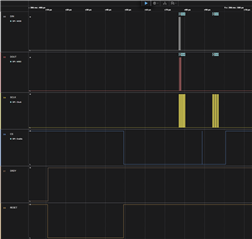

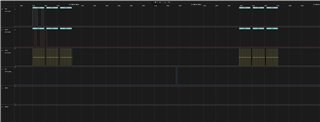

此外、我还添加了逻辑测试。 在这里、我尝试读取 ID 寄存器(00h)、 我预计可以看到位15:8的值、即值(24h)、但我得到了这个值。 另外、我发现在 MISO 线上看到的脉冲与 CLK 线上的脉冲相似、这很奇怪、但我已经检查了它们是否没有相互连接。 实际上、当我发送第一个位时、MISO 线和 CLK 线之间的值是不同的。 我真的不知道这些脉冲为什么出现在 MISO 线上。