Other Parts Discussed in Thread: CDCE62005, DAC3484, DAC3482

Thread 中讨论的其他部件:CDCE62005、和 DAC3482

工具/软件:

你好

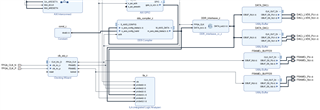

我正在配置一个包含 FPGA 板(Avnet Microzed 7020)的系统、该板连接到包含2个 DAC3484和一个 CDCE62005的定制板。

我的初始目标是了解单个 DAC 的利用率、我尝试接收由我的 NCO (+ DDS 的相位)提供的5MHz 正弦波的输出(由我的示波器测量)。

FPGA 板配置为以符号幅度表示形式输出16位数据信号、其中上升沿显示正弦波相位、下降沿显示余弦波相位作为输出。

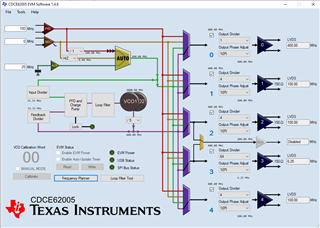

我的 CDCE62005配置(连接到100MHz 的主时钟):

0xEB40032、//寄存器0- DACCLK1 400MHz

0xEB84030、//寄存器1- DACCLK2 100MHz (目前不相关、因为我专注于 DAC1)

0xEB84030、//寄存器2-不相关

0xEB3C030、//寄存器3--OSTR 6.25 MHz

0xEB84031、//寄存器4- FPGACLK 100 MHz

0x10080BF、//寄存器5

0x04BE008、//寄存器6

0xBD0037F //寄存器7

DAC 配置:

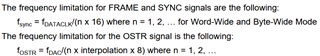

阅读数据表、我得到了以下公式:

因此、F_OSTR=F_FRAME= 6.25MHz = F_DACCLK/64

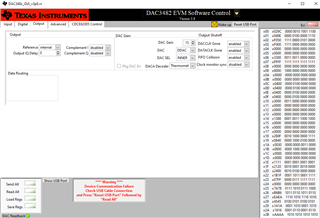

DAC 的输入仅使用两个通道、因此我启用了双模式、并使用示波器测量了 B 通道。

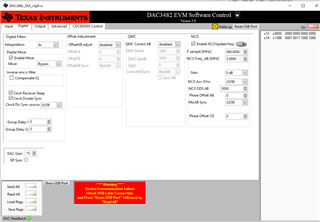

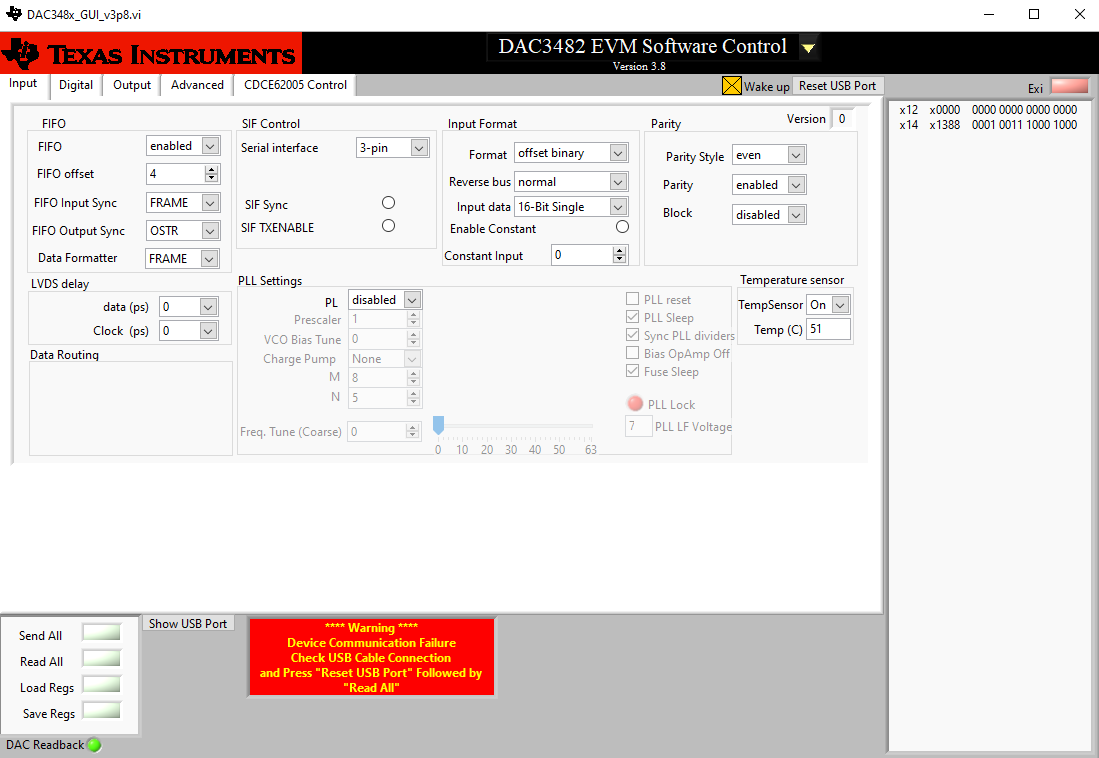

我禁用了 PLL (config24/bit10->0)、在 config31控制(0x2220)中选择 OSTR 作为同步源、并启用了混频器和 NCO (config2:0xF050)。

有关我的系统的其他信息:

* F_DATACLK= 100MHz

*插值为4

* NCO 相位字为0x03333333

*我的 FPGA 系统的相关部分如下所示:

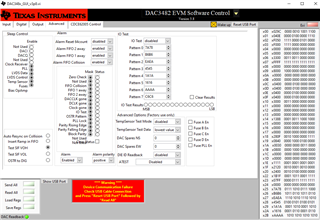

*我的 DAC 配置:

x00 x029F 0000 0010 1001 1111

x01 x050E 0000 0101 0000 1110

x02 xF070 1111 0000 0111 0000

X03 xF001 1111 0000 0001

X04 x0000 0000 0000 0000 0000

X05 x0000 0000 0000 0000 0000

X06 x3300 0011 0011 0000 0000

x07 xFFFF 1111 1111 1111 1111

X08 x0000 0000 0000 0000 0000

x09 X8000 1000 0000 0000 0000

x0A x0000 0000 0000 0000 0000

x0B x0000 0000 0000 0000 0000

x0c x0400 0000 0100 0000 0000

x0D x0400 0000 0100 0000 0000

x0E x0400 0000 0100 0000 0000

x0F x0400 0000 0100 0000 0000

x10 x0000 0000 0000 0000 0000

x11 x0000 0000 0000 0000 0000

x12 x0000 0000 0000 0000 0000

x13 x0000 0000 0000 0000 0000

X14 x3333 0011 0011 0011 0011 0011

x15 x0333 0000 0011 0011 0011

x16 x6666 0110 0110 0110 0110

X17 x2666 0010 0110 0110 0110

x18 x280F 0010 1000 0000 1111

x19 x0840 0000 1000 0100 0000

x1A x0030 0000 0000 0011 0000

x1B x0800 0000 1000 0000 0000

x1C x0000 0000 0000 0000 0000

x1D x0000 0000 0000 0000 0000

x1E x1111 0001 0001 0001 0001 0001

x1F x1110 0001 0001 0001 0000

x20 x2401 0010 0100 0000 0001

x22 x1B1F 0001 1011 0001 1111

X23 x07FF 0000 0111 1111 1111

x24 x0000 0000 0000 0000 0000

X25 x7A78 0111 1010 0111 1000

X26 xB6B6 1011 0110 1011 0110

x27 xEAEA 1110 1010 1110 1010.

X28 x4545 0100 0101 0100 0101

X29 x1A1A 0001 1010 0001 1010

X2A x1616 0001 0110 0001 0110

x2B xAAAA 1010 1010 1010 1010 1010.

x2C xC6C6 1100 0110 1100 0110

x2D x0004 0000 0000 0100

x2E x0000 0000 0000 0000 0000

x2F x0000 0000 0000 0000 0000

x30 x0000 0000 0000 0000 0000

x7f x0000 0000 0000 0000 0000

*设置和重置 CDCE 后,无论4.27MHz 的 DDS 输出如何,我都会得到一个稳定的正弦波。 由于某种原因,我不能添加更多的图片到我的帖子,所以我无法显示它。

一些问题:

1.在启动时进行模式检查有多重要?

2.出于某种原因,在 config2中设置"二进制"位会导致所有输出中断,为什么会这样?

3. DAC 的配置可能会出现什么问题。

提前感谢您、

Tom