工具/软件:

在使用了 15 年的设计中、我们发现用于数据采集的模拟缓冲区太慢。 现在、我们希望以简单的方式延长数据采集时间。

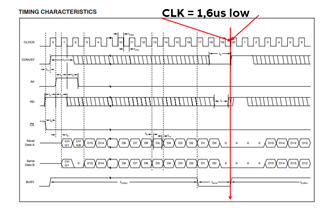

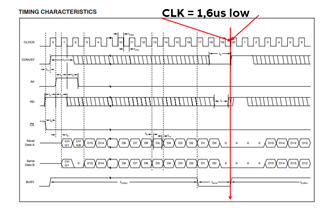

时序: CLK 周期:125ns

M0、M1 =低电平

对于数据采集、我们希望将时间从 400ns 增加到 2us。

1) 我们可以在下一次转换开始之前创建 16 个额外的 CLK 吗?

2) 我们可以在 CLK19 处插入 2us 的低暂停、然后继续转换开始。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

在使用了 15 年的设计中、我们发现用于数据采集的模拟缓冲区太慢。 现在、我们希望以简单的方式延长数据采集时间。

时序: CLK 周期:125ns

M0、M1 =低电平

对于数据采集、我们希望将时间从 400ns 增加到 2us。

1) 我们可以在下一次转换开始之前创建 16 个额外的 CLK 吗?

2) 我们可以在 CLK19 处插入 2us 的低暂停、然后继续转换开始。

您好、Guenther、

欢迎来到 TI 的 E2E 论坛! 感谢您发送编修。

我先回答主线程中的问题:

1) 我们可以在下一次转换开始前创建 16 个额外的 CLK 吗?

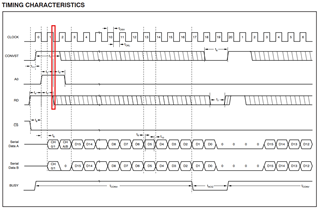

是的、只要只有前 20 个时钟被视为对数据有效(遵循数据表中的表 III)、这应该没问题。

2) 我们可以在 CLK19 处插入 2us 的低暂停、然后继续转换开始。

是的、也会像您预期的那样将 ADC 保持在采集时间。

更改:12 个额外时钟

是在添加 12 个时钟还是插入低暂停之间进行选择? 两者都应正常工作。

我们在 RD 和 Conversion Start 的同时设置 A0。

只要在 时钟 1 的下降沿(从 CONVST 上升沿开始的第 2 个下降沿)之前至少配置 15ns 并在工作后 15ns 保持该状态、就根本不是问题。

A0 的状态在第一个时钟周期的下降沿被锁存、为了确保正确的值被锁存、有一个±15ns 的范围来确保正确的设置和锁存。 T2 和 T3 的时间仅被指定为最小值、因为超出这些时间理论上可以是任何值。

此致、

Yolanda