工具/软件:

尊敬的团队:

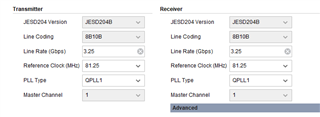

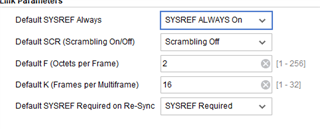

我使用 adc12dj5200s 的 DDC 模式、ADC 的时钟为 5.2GHz。我使用 jmode16 将采样率降低到 650MSPS。在 FPGA 中、jesd204b 的配置如下图所示。并且 jesd204b 的核心时钟为 81.25MHz、Sysref clk 为 5.078125MHz。

和 ADC 寄存器列表 、如下图所示。

24'h0000B0、//SOFT_RESET、最后自行清除 750ns

24'h002B15、//所有时间默认值

24'h02A230、//所有时间设置

24'h02C200、//不会屏蔽所有警报

24'h020000、//JESD_EN = 0

24'h006100、//CAL_EN = 0

24'h0220CA、//FREQA0

24'h022139,

24'h0222D9、

24'h022349,

24'h020110、//JMODE = 16

24'h02020F、//K=16

24'h020500、//TEST_MODE、0:normal

24'h006001、//所有时间默认值

24'h021500、//选择 4 个 NCO 中的哪一个用作活动 NCO。[3:2] CSELB 和[1:0] CSLA。 范围:0-3 00:对 CHA 和 CHB 使用 nco0

24'h020400、//8b/10b OFFSET_BINARY USE_syncse_pin:all time 默认值

24'h002920、//设置 sysref_recv_en =1

24'h002960、//set sysref_proc_en = 1 且 sysref_recv_en = 1

24'h002970、//set sysref_proc_en = 1 且 sysref_recv_en = 1、放大 sysref 窗口状态、较小的延迟

24'h002969、//根据 sysref_pos 设置 sysref_delay

24'h006101、//CAL_EN = 1

24'h020001、//JESD_EN = 1

24'h006C00、//CAL_SOFT_TRIG = 0

24'h02C100、//警报标志、如果=1.警报激活

24'h006C01、//CAL_SOFT_TRIG = 1;格式 0 至 1 表示 CAL_TRIG 生成、开始校准。

延迟 100 μ s

24'h021902,

24'h021903

根据上述配置、NCO 频率约为 1.5GHz、无法稳定建立我的 jesd204b 链路、SYNC 信号会频繁跳转。但奇怪的是、如果我没有配置 FREQA0 寄存器并保持其默认值 0xc000000、仍然可以正常稳定地建立链路。

我不知道如何解决这个问题、您能帮我吗?

期待您的答复!