Other Parts Discussed in Thread: DAC8760

Thread 中讨论的其他器件:DAC8760

工具/软件:

dera 支持

我们正在设计适用于 DAC8750 的电路。 我们有一个关于未使用引脚的问题。 如果我们未使用 ISET-R 引脚、HART-IN 引脚以及 CAP1 和 CAP 引脚的功能、是否可以将其保持未连接状态?

另外、如果我们使用内部 RSET、是否可以将控制寄存器 DB13 (REXT) 设置保留为默认值?

谢谢你

此致

Yusuke

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: DAC8760

工具/软件:

dera 支持

我们正在设计适用于 DAC8750 的电路。 我们有一个关于未使用引脚的问题。 如果我们未使用 ISET-R 引脚、HART-IN 引脚以及 CAP1 和 CAP 引脚的功能、是否可以将其保持未连接状态?

另外、如果我们使用内部 RSET、是否可以将控制寄存器 DB13 (REXT) 设置保留为默认值?

谢谢你

此致

Yusuke

Yusuuke-San,

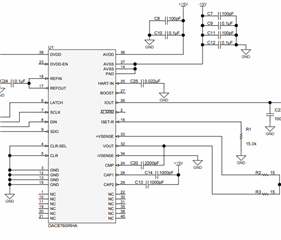

CAP1 和 CAP2 引脚可保持未连接状态。 这些引脚上的电容用于对器件的输出进行滤波、您可以看到当数据表的图 8-4 和图 8-6 中添加这些电容时、稳定时间的变化。

如果使用了内部设定电阻器、ISET-R 也可保持未连接状态。 如果您使用的是内部电阻器、则可以将控制寄存器的 DB13 保留为 0、就像您在上一次发布中提到的那样。

如果不使用 HART、我会通过一个 22nF 电容器将 HART-IN 引脚接地。

如果您有任何其他问题、请告诉我。

Joseph Wu

Yusuuke-San,

我想这不会有问题。 但是、由于节点的阻抗稍高 (~35kΩ)、因此我通常想确保有一条低阻抗、高频的接地路径。 我需要担心的是、如果该节点悬空、EMI 可能会产生一些噪声、这会导致输出发生一些变化。

对于该器件 (DAC8760) 的电流/电压版本、我们提供了经过 EMC 测试的 EVM 版本。 您可以在此处找到 EVM 信息:

https://www.ti.com/lit/ug/sbau229/sbau229.pdf

对于您提到的所有引脚、每个引脚都有连接:

但是、我认为 HART-IN 引脚具有最高的输入阻抗、并且更容易受到 EMI 的影响。 因此、我认为在该节点处使用 220nF 电容比其他节点更重要。

Joseph Wu

此外、有一个 TI 设计详细描述了此 EVM。 您可以在此处找到设计文件夹:

https://www.ti.com/tool/TIPD153

以及此处的设计指南:

https://www.ti.com/lit/pdf/tidu011

Joseph Wu