工具/软件:

您好、

从 ADC 获取 16 位数据 o/p、而不是 20 位、因为从 SPI 读取值需要 20 个 SCLK。

模式引脚 M0 = 0、M1 = 1、A0 = 0

基准 =内部基准 2.5V

SPI 处于仅接收模式、频率为 10MHz。

i/p 电压 数据值

1.2744 五 0x8280

1.0021 伏 0x65c0

0.5079 伏 0x3464

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 Priti、

您能否在数据传输期间分享一个逻辑分析仪或数字引脚示波器的屏幕截图? 还提供原理图吗?

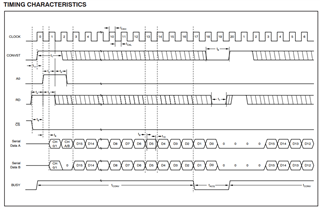

ADS8361 是一款 16 位 ADC、因此数据输出应为 16 位。 数据传输应采用 20 位格式、这意味着它需要 20 个时钟、第一位表示多路复用器通道编号(M0 = 0、M1 = 1、A0 = 0、这将是通道 0,使此位为逻辑低电平)、然后是 ADC 通道(在 CHA 和 ChB 之间切换)、最后是 16 位 ADC 数据、最后 2 位设置为 0。

此致、

Yolanda

您好 Priti、

从我在您的示波器中可以看出、数据看起来是 CHA0:0x1BE4、与 CHA0 上的输入相关、该值应约为 544mV?

您能否分享包含 CONVST 信号的另一个示波器快照? 时序可能关闭、器件收到 19 个时钟而不是 20 个时钟。 根据 CONVST 的不同、数据可能会移位 1 位、该值可能~270mV?

我还注意到时钟配置了 CPOL 设置为 1(空闲时时时时时时时时钟极性设置为高电平)、您控制器中的时钟相位设置是什么?

在 SDO 上、数据位在 SCLK 的上升沿转换、应在 SCLK 的下降沿读取。 您能否确认您的控制器遵循什么协议? 并确保在 SCLK 的下降沿捕获数据?

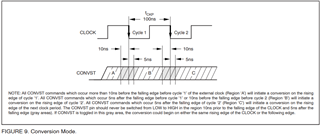

另一个需要注意的重要事项是第 1 个下降沿、这与 CONVST 耦合是启动转换并设置数据在哪个周期有效。 根据 CONVST 的上升沿与 SCLK 的下降沿之间的关系、SDO 上的数据将在下一个 SCLK 上升沿或之后的上升沿开始转换(图 9 对此进行了更接近的说明)。 您是否能够测试这个时序? 这有助于确保器件也能获得完整的 20 个时钟。

如果您测量 CHA/B 的 CH1、则第 1 位应为 1、可以帮助确定有效数据的开头位置。

此致、

Yolanda

您好 Priti、

感谢您分享这些屏幕截图。

最后一幅图 (SCLK 和 DOUT) 是否具有不同的输入电压(不是顶部提到的 1V)? 该图片上的 DOUT 看起来与 CONVST 和 DOUT 图像上的 DOUT 非常不同。

ADC 的输入是什么样子的?

我看到所有输入都有一个“_N"和“和“_P",“,使、使其看起来是差分的、您的输入信号的共模是多少?

如果您使用 CPOL = 1、我建议您将 CPHA 设置为 0、以便控制器在下降沿读取有效 SDO 数据、并忽略第一个下降沿。

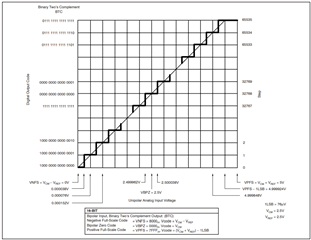

下面是我如何尝试解码 SCLK 和 DOUT 示波器屏幕截图上的数据、0x02F6 看起来更像是比信号的共模高~50mV(如果共模= 2.5V、则为~2.55V)。

我 也尝试了解码 CONVST 和 DOUT、但由于其他两个示波器屏幕截图的时间均为 5us/div、其中一个为 10us/div、因此难以确认。 您能否在示波器上具有相同的输入和相同的时间/div 条件下分享一些类似的内容?

此致、

Yolanda