Other Parts Discussed in Thread: ADC12DJ1600, ADC12QJ1600

主题中讨论的其他器件: ADC12QJ1600

工具/软件:

(l) 您好、

我想在 JMODE9 中配置双核 ADC12DJ1600、但仅使用第一个内核。

应如何配置 FPGA IP 以支持该功能? 尤其是使用车道 (L) 参数时?

在相关主题中、我通过将通道 (L) 参数从 8 更改为 2、设法使四通道器件 ADC12QJ1600 在 FPGA IP 中仅启用第一个内核的情况下运行。

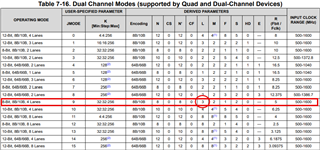

双器件的数据表中将“Lanes (L)“参数指定为 3。 为什么会这样? 我本以为它是 4??

应如何更改它以处理仅运行的第一个内核?