Other Parts Discussed in Thread: DAC39RF12EVM

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DAC39RF12EVM

工具/软件:

尊敬的 TI 支持团队:

我目前使用的是 DAC39RF12EVM。

在套件的默认配置中、采样时钟作为单端信号提供给 DAC_CLKp 端口。

我想同时使用 DAC_CLKp 和 DAC_CLKn 端口以差分方式配置采样时钟输入。

但是、我在用户指南或数据表中找不到有关此配置的详细说明或指导。

您能否说明差分时钟输入是受支持的配置还是推荐的配置?

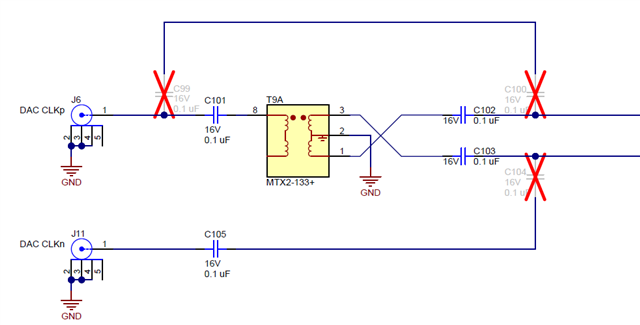

根据原理图、似乎可以通过移除 C101、C102 和 C103 电容器来实现差分时钟输入、

并重新填充 C99、C100 和 C104 位置的电容器。

您能否确认这是否是启用 DAC 的差分时钟输入的适当有效方法?

如果没有、请您就正确的程序提供指导。

感谢您的支持。