工具/软件:

您好:

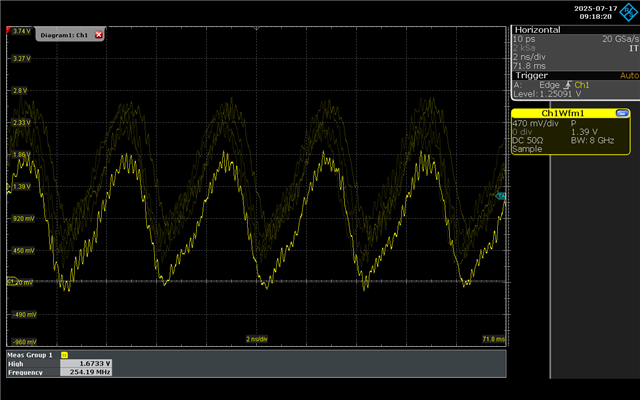

我期望 DCLKI 输出在 1:2 DMUX 模式下始终具有 50%的占空比、频率为 FS/4。 您能否确认 DCLKI 始终具有 50%的占空比?

我有一个对 DCLKI 敏感的 VHDL 过程、在测试中、该过程会生成另一个时钟、如下所示:

P_COMBLE_ADC_SAMPLES_RISING:进程 (I_DCLKI、RESET_n)

变量 yy : std_logic :='0';

开始

如果 RISING_EDGE (I_DCLKI) 且 RESET_n =“1",“,则、则

yy:=不是 yy;

GPIO (4)<= not yy;

......

谢谢你