工具/软件:

您好、

ADC 的数字输入没有标准电压电平。

1.8V 时的 FPGA ADC/VIL VOL 不支持 VOH VIH/VIL。

如何 在+2/–2mA 电流驱动中定义 FPGA 电平。

没有定义低电流下的电压电平、这可能是 ADC 中的情况。

请 建议如何驱动此线路?

此任务是否需要专用的外部驱动程序?

此致

Zeev Gerber

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

ADC 的数字输入没有标准电压电平。

1.8V 时的 FPGA ADC/VIL VOL 不支持 VOH VIH/VIL。

如何 在+2/–2mA 电流驱动中定义 FPGA 电平。

没有定义低电流下的电压电平、这可能是 ADC 中的情况。

请 建议如何驱动此线路?

此任务是否需要专用的外部驱动程序?

此致

Zeev Gerber

尊敬的 Zeev:

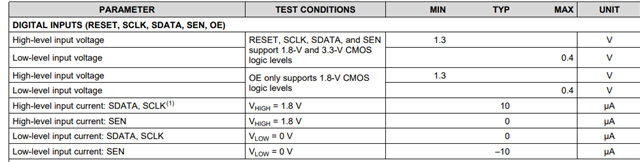

您能告诉我您指的是哪些数字引脚吗? VIH 和 VIL 电平位于下表(表 7.8)中、可以在数据表的第 14 页中找到。

此致、

Geoff