主题中讨论的其他器件: SN74LV1T34

工具/软件:

您好 TI

我在 1 时使用 SCLK_SEL、在 1 时使用 LL_CONFIG、在 0 时使用 FPATH。

FAE 告诉我控制 START 终端、使用 256kHz 的采样频率。

我正在考虑向 CLK 端子输入一个 16.384MHz 的频率、但我想知道 START 信号和 DRDY 信号之间的延迟时间 (tsettle)。

我正在考虑将 DRATE 设置为“11"或“或“10"。“。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好 TI

我在 1 时使用 SCLK_SEL、在 1 时使用 LL_CONFIG、在 0 时使用 FPATH。

FAE 告诉我控制 START 终端、使用 256kHz 的采样频率。

我正在考虑向 CLK 端子输入一个 16.384MHz 的频率、但我想知道 START 信号和 DRDY 信号之间的延迟时间 (tsettle)。

我正在考虑将 DRATE 设置为“11"或“或“10"。“。

你好、Shota Nuki、

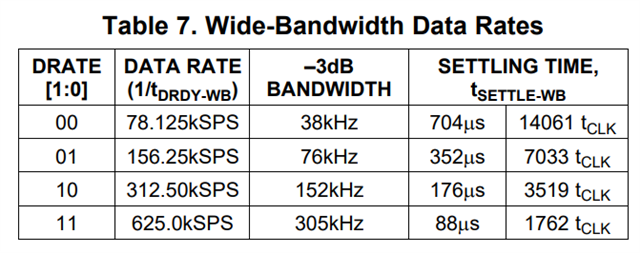

您可以使用 START 引脚来控制转换、但数据速率将受到数字滤波器稳定时间的限制。 在本例中、您已配置具有宽带滤波器的 ADS1672。 在这种情况下、 表 7 指定了滤波器的稳定时间和有效数据速率。

在您的情况下、使用 fCLK=DRATE='11'和 16.384MHz、稳定时间将为 1762*(1/16384000)=107.54us。 使用 START 引脚进行单次转换(图 23)、在此配置中可支持的最快数据速率为 Fdata=1/107.54us=9.299kSPS、比此 DRATE 设置的连续转换速率慢得多。

如果您希望支持 256kSPS、则需要在连续转换模式下使用 ADS1672、其中 START 引脚持续保持高电平、如图 35 所示。

对于 256kSPS 数据速率、可以使用 DRATE='10'并调整时钟频率。 DRATE='10'的 fCLK/Fdata(过采样率或 OSR)之比为 64。 根据您确定、支持 256kSPS 所需的时钟频率将为 16.384MHz。

此致、

Keith Nicholas

精密 ADC 应用

你好 Nicholas

谢谢你。

最初,我考虑将起始端子固定在 H 和 256kHz,并询问 FAE ,但被告知,这是不可能的,除非它是由起始端子控制。

感谢您这次查询、将起始端子固定为 H 没有问题。我想做的是在 tDRDY 的 3.90us 内从 DOUT 读取 24 位数据。 因此、我计划从 FPGA 提供 8.192MHz SCLK。

我附上了计时表、我认为这是可能的、但这是正确的吗?

顺便说一句,我想把 CS 固定在 L

你好、Shota Nuki、

是的、您可以将 CS 修复为低电平。 这将减少 ADC 和处理器之间的控制线数。 由于串行端口将始终启用、因此请确保 SCLK 是干净的信号、并且具有非常小的下冲/过冲。 否则、您可能与串行端口不同步、在这种情况下、您需要对 START 引脚施加脉冲来复位器件和转换。

是的、您可以使用 SCLK 频率 8.192MHz、这将允许根据您的配置在 1 个数据速率周期内读取 24 位转换结果。

此外、我强烈建议将 START 引脚连接到 FPGA、以确保上电后器件正常运行和同步。

另请注意、CLK 输入以 AVDD 为基准、并且必须为 5V CMOS 电平。 如果需要、您可以使用电平转换器、因为许多振荡器都以 5V 电压运行。 其余数字引脚以 DVDD 为基准 (2.7V 至 3.3V)。

此致、

Keith

谢谢你。

另外、感谢您查看时序图。 我使用五个 ADS1672、并希望在每个器件之间同步采样时序、因此我想通过 FPGA 控制 CLK、SCLK 和 START 端子。 FPGA 将与每个器件一对一通信。 我将在每个信号中插入阻尼电阻器以移除 OS/US。

我知道 CLK 也需要控制在 5V。 FPGA 输出为 3.3V、因此我将使用电平转换器。 如果您有任何推荐的 IC、请告诉我。