Other Parts Discussed in Thread: ADS1672, SN74LV1T34

主题中讨论的其他器件: SN74LV1T34

工具/软件:

您好 TI

我在 1 时使用 SCLK_SEL、在 1 时使用 LL_CONFIG、在 0 时使用 FPATH。

FAE 告诉我控制 START 终端、使用 256kHz 的采样频率。

我正在考虑向 CLK 端子输入一个 16.384MHz 的频率、但我想知道 START 信号和 DRDY 信号之间的延迟时间 (tsettle)。

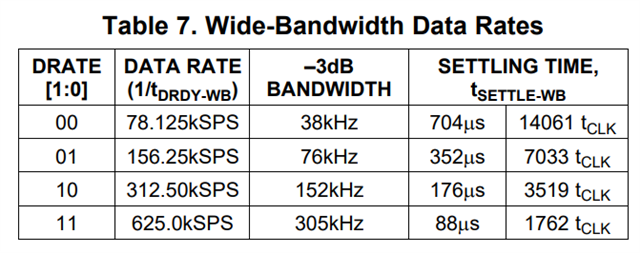

我正在考虑将 DRATE 设置为“11"或“或“10"。“。