Other Parts Discussed in Thread: LMK04832EVM, ADC3683, LMK04832, ADC3683EVM

主题中讨论的其他器件: LMK04832、LMK04832EVM 、

工具/软件:

尊敬的 TI:

我将使用 LMK04832 通过交流耦合到 7(七个)ADC3683 芯片来提供 65MHz LVPECL 时钟信号、所有这些芯片都放置在单个 PCB 上。 该应用是“相位计“、其中低固有相位噪声是关键要求。

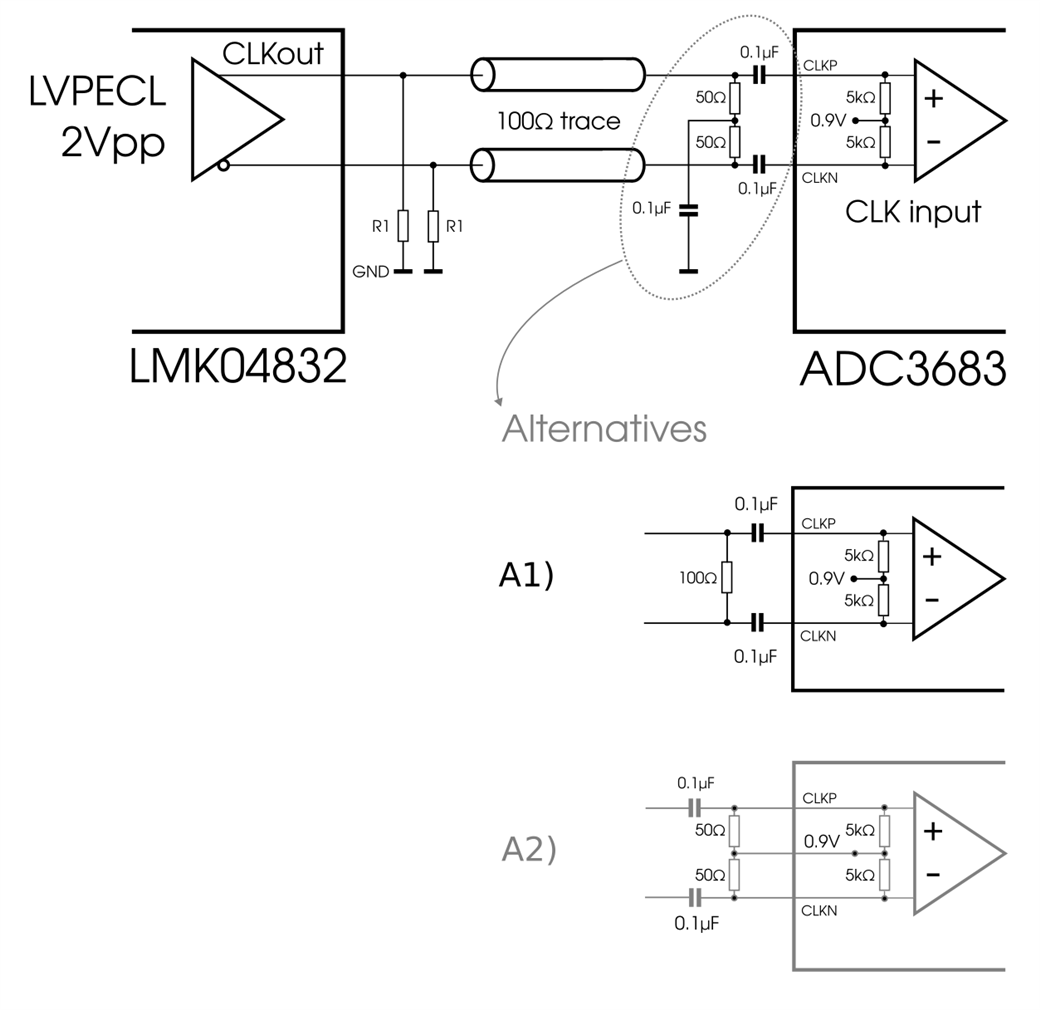

请考虑下图:

我会有这些非常微妙的问题:

.:1) LVPECL 驱动器直流路径和 R1 值:

根据 SLLA112、R1 的电阻值应在 140 至 220 欧姆之间。 根据 SNAU215A、LMK04832EVM 上使用的值为 120 Ω 和 240 Ω(某些通道上有 120 Ω 电阻器、其他通道上有 240 Ω 电阻器)。 由于我希望在 AD 转换期间实现高 SNR/SFDR、因此根据 ADC3683 数据表 SBAS872B 及其图 8-14、更高的时钟振幅是有益的。 因此、我倾向于选择较小的 R1 值来增加电流、从而增加 ADC3683 时钟输入端的差分电压。 因此、我选择 R1 为 120 欧姆。 您同意吗? 或者从某种角度来看、240 欧姆电阻是更好的选择?

.:2) ADC3683 侧差分时钟路径的端接

上图所示传输线路末端的端接取自 ADC3683 评估板的原理图(DC134-004-Reve_SCH.pdf、TI 网站上的“ADC3683EVM 设计文件“中提供)。 我想知道所显示的备选方案 A1) 和 A2) 是否也可以考虑。 A1) 对于使用的元件数量较少似乎是一个合理的选择、根据 SLLA112(如果我正确地解释)、这个选项非常适合没有差分偏斜和共模噪声的情况。 即使所有元件都放置在单个 PCB 上、它也可能无法完全应用于实践中。 A2) 的动机是 ADC3683 共模电压输出引脚的可用性;然而、这可能是一个不好的主意、因为它会显著改变 ADC3683 内的工作点(通过并联添加 50 Ω 至 5k Ω 电阻器)。 因此,我会坚持原来的解决方案(上图的顶部),不会使用替代方案 A1) 或 A2)。 您同意吗?

.: 3 CML 而不是 LVPECL?

使用 CML 而不是 LVPECL 在 65MHz 进行时钟采样是否有任何好处? 我知道、对于更高的频率(例如 1GHz 以上)、CML 可能会提供更好的相位噪声 (LMK04832 数据表 SNAS688C 指出“旁路模式下 CML 可实现最佳性能“)。 我认为、对于如此低的采样频率、这两个标准之间在相位噪声方面的差异可能可以忽略不计、这是正确的吗? 此外、我更喜欢 LVPECL、因为它使用的驱动电流似乎比 CML 更低、因此可能会产生微小的自干扰。 这些想法在某种程度上合理吗?

非常感谢!

Ondrej