Other Parts Discussed in Thread: ADC12QJ1600, TSW12QJ1600EVM, TSW14J58EVM, THS4541

主题中讨论的其他器件:TSW12QJ1600EVM、ADC12QJ1600、 THS4541

工具/软件:

尊敬的 exparts:

TSW12QJ1600EVM 数据表提供了使用 TSW14J58EVM 的说明。

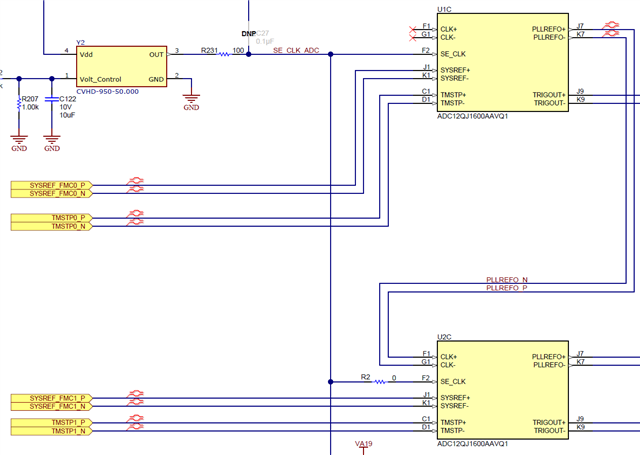

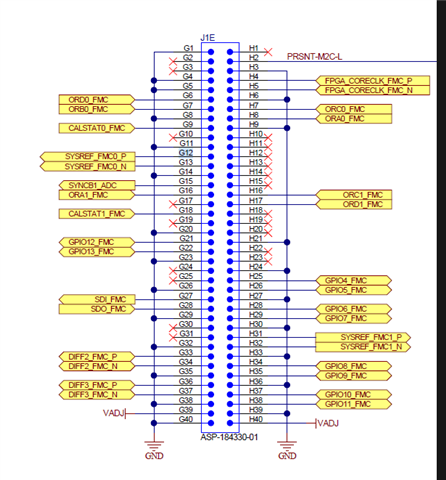

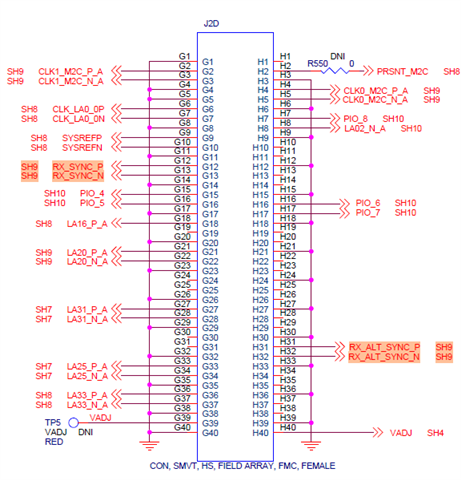

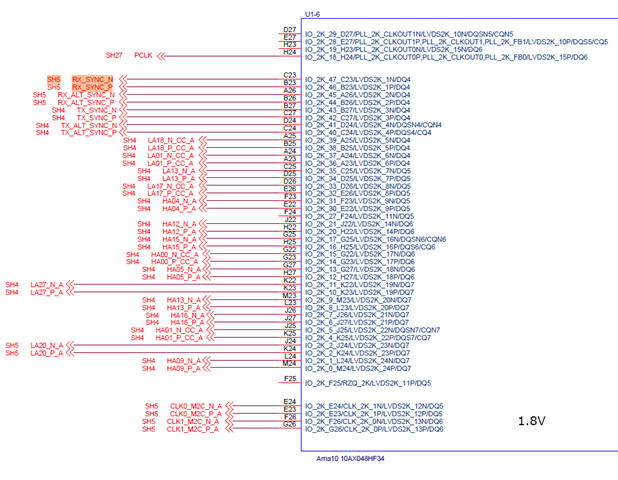

TSW12QJ1600EVM 两个 ADC 的 SYSREF +/-分别连接到 FMC 连接器。 (G12、13、H31、32 引脚)

TSW14J58EVM 侧的引脚 (G12、13、H31、32) 直接与 FPGA (XCKU5P) 相连。

您能告诉我这个器件的 I/O 设置吗?

此致、

Hiromu