工具/软件:

我们正在硬件配置模式下使用 ADS8528 进行串行数据传输。

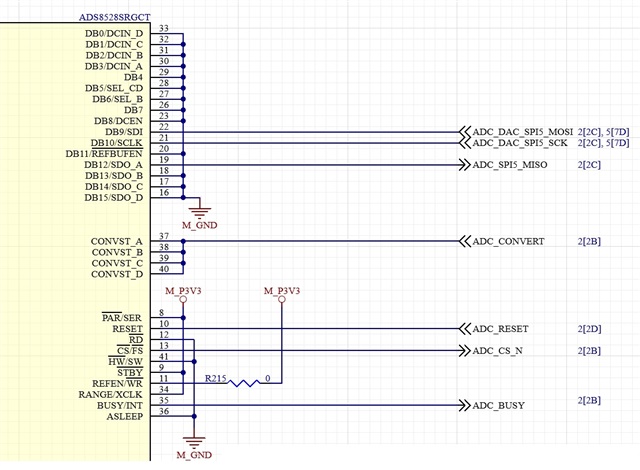

有关 SPI 连接的信息、请参阅原理图。

数据表中显示了 ADS8528 通道 (CH_A0、CH_A1、CH_B0、CH_B1、CH_C0、 CH_C1、CH_D0、CH_D1) 成对分组、数据可以通过 SDO_A、SDO_B、SDO_C 和 SDO_D 成对串行卸载。 我们的设计配置为通过 SDO_A 输出串行输出所有 8 个通道。

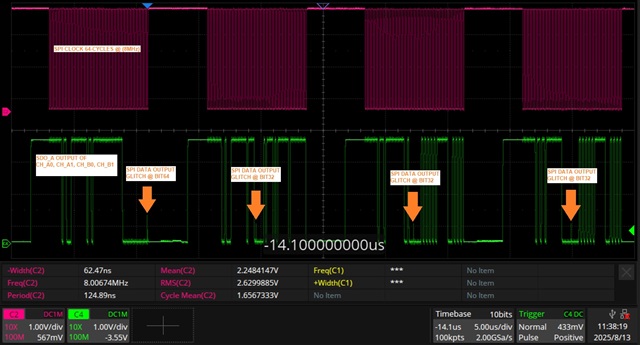

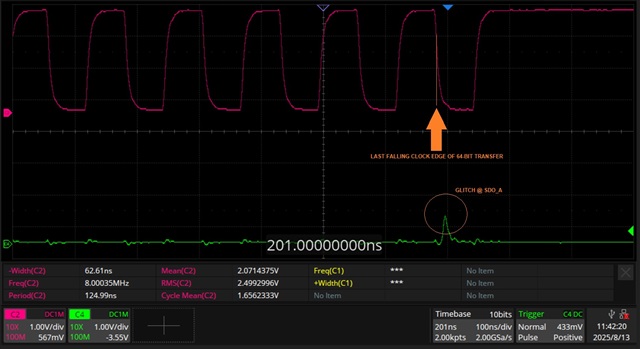

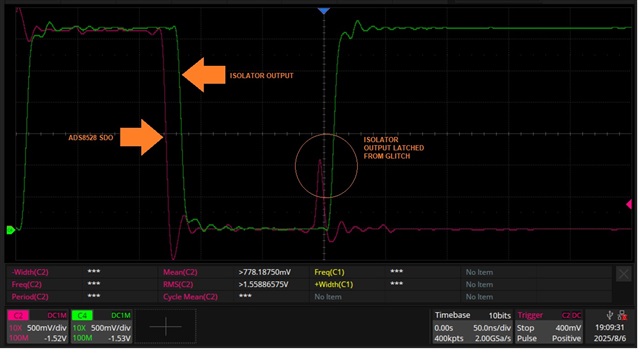

当读取串行数据输出时、数据传输的 32 位和 64 位边界处似乎存在“干扰“。

我在 SDO_A 处附上了 SPI 时钟和串行数据输出的示波器图 虽然我们正在对全部 8 个通道进行采样、但在本例中、我们只读取前四个通道 (CH_A0、CH_A1、CH_B0、CH_B1)。 因此、这些图显示了 64 位传输组(通道 CH_A0、CH_A1、CH_B0 和 CH_B1)。

ADS8528 是否会成为“干扰源“?

是否存在干扰是 ADS8528 的产物、任何内部寄存器切换都允许通过单个 SDO_A 端口输出所有通道?