Other Parts Discussed in Thread: DAC3162, DAC3162EVM, SN65LVDS100

主题中讨论的其他器件:、 SN65LVDS100

工具/软件:

你好

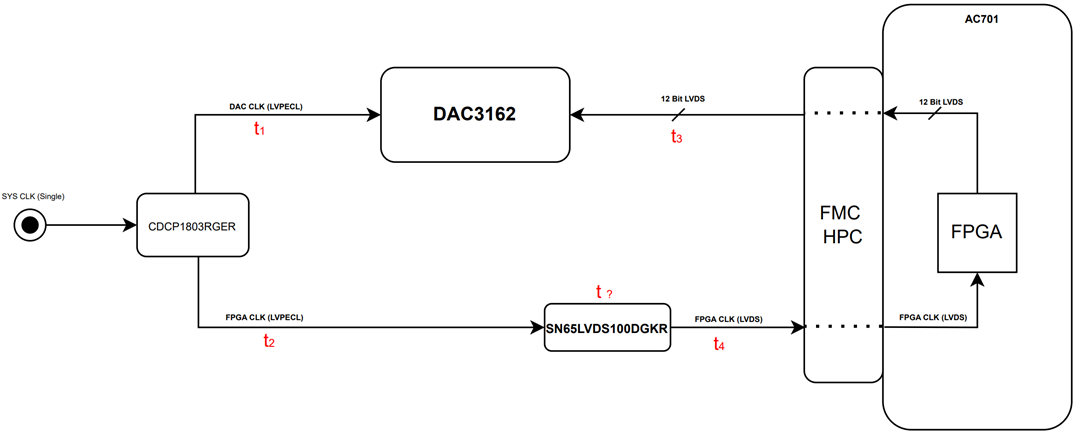

我正在设计具有 FMC 接口的 PCB 板、包括 DAC3162。 我在设计中使用 DAC3162EVM 和 FMC 适配器卡作为参考。

该板将通过 FMC 连接器连接到 AC701 FPGA 板。

它还包括一个 LVPECL 至 LVDS 缓冲器 (lvds100dgkr) 集成电路、用于在 FPGA 上作为 LVDS 接收 LVPECL 时钟信号。

我不知道在 PCB 上进行长度匹配时如何调整延迟时间。

数据表指出建立时间和保持时间应至少为 200ps。

在 PCB 设计中、为了实现这种延迟、应考虑哪些因素?

为了更好地理解、我添加了方框图。 目前、延迟值大致如下:

T1 = T2 = 360ps

T4 < 10ps

T3 = 300PS

我相信 FPGA 板上的线路具有等效的延迟。

此外、我应该如何考虑 SN65LVDS100 集成电路的内部延迟?

我需要帮助确定时钟线和数据线的延迟值。

谢谢你。