主题中讨论的其他器件:DAC38J84

工具/软件:

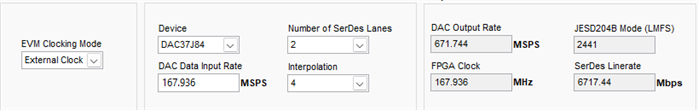

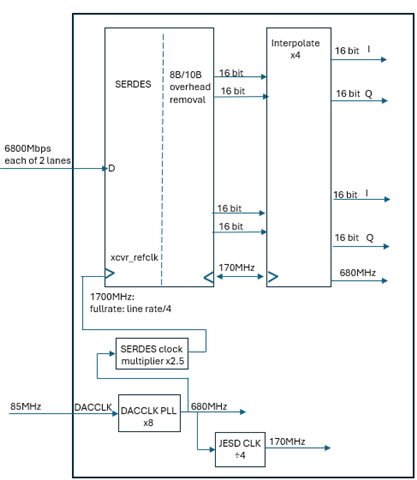

我们将在两个 JESD 通道上传输 170Msps x 64、如下所示(两个 DAC 输出均为 16 位 I/Q)

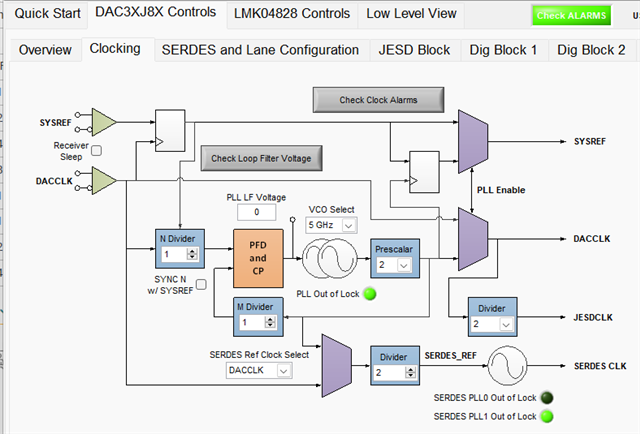

我假设 JESDCLK 应为 170MHz (4 分频、config37=0x4000)、如下所示。

但是、必须将其设置为 340MHz (2 分频、config37=0x2000) 才能正常工作。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好:

请使用 DAC38J84 配置 GUI 来设置内部 JESD204 时钟。 设计人员将内部 JESDCLK 设置为使 DAC38J84 更高效地配合使用、并且在方框图级别不一定最直观

我们正在使用 GUI、它会要求用户识别该频率。 此时钟位于 DAC 内部、仅在内部使用、没有关于要设置哪个频率的指令。 效率不是问题、设置为 340MHz 时它运行良好、在 170MHz 完全不工作。 由于它称为 JESD CLK、因此合乎逻辑的是、它将以从 JESD 块提取数据并传输到内插器的速率运行。 但是、我展示的方框图必须是对器件内部运行情况的假设。

考虑到我所描述的内容、如何确定将该时钟设置为什么?

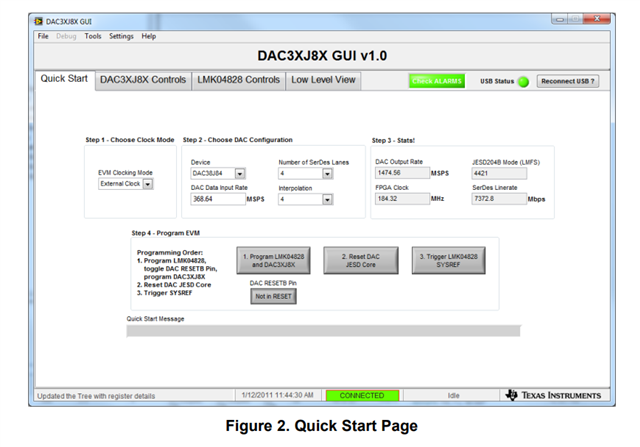

您好、David、

在快速入门页面输入 DAC38j84 所需的配置后、系统会自动为您配置 JESD CLK。 clkjesd_div 设置全部计算得出。

根据 JESD204B RX 逻辑块的 JESD204B 配置设置、需要相应地调整 JESD204B RX 逻辑块的参考时钟。 有关时钟分频器设置的详细信息、请参阅下表。

|

DAC3xJ8x JESD204B RX 逻辑时钟分频器设置 |

|||||

|

配置 37、位 15 至 13、 clkjesd_div |

|||||

|

进行内插 |

|||||

|

LMF 模式 |

1x 内部 |

2 倍插值 |

4 倍插值 |

8 倍插值 |

16 倍插值 |

|

841. |

2. |

4. |

8. |

16 |

32 |

|

442. |

1. |

2. |

4. |

8. |

16 |

|

244. |

不适用 |

1. |

2. |

4. |

8. |

|

148. |

不适用 |

不适用 |

1. |

2. |

4. |

|

821 |

4. |

8. |

16 |

32 |

不适用 |

|

421. |

2. |

4. |

8. |

16 |

32 |

|

222. |

1. |

2. |

4. |

8. |

16 |

|

124. |

不适用 |

不适用 |

2. |

4. |

8. |

好的、我理解、谢谢。

Quick Start 页面假设 DACCLK 不会被 PLL 转换为 freq (N 分频器除以 2、预分频器乘以 2)、如下所示。

鉴于频率较低的输入 DACCLK 和从 PLL 时钟得出的 SERDES REF、我认为需要重新计算本页上的所有内容。

但是、我需要重新计算*除 JESDCLK 分频器之外的所有内容。

感谢您清除此内容。

Dave