主题中讨论的其他器件:TSW14J58EVM、、

工具/软件:

使用 ADC32RF55EVM 和 TSW14J58EVM 对 ADC 进行评估。

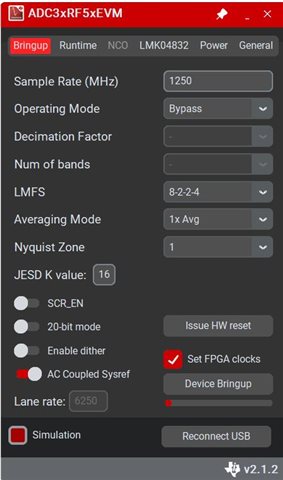

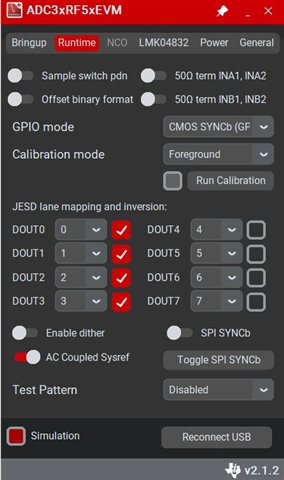

ADC3xRF5xEVM-GUI 工具用于将寄存器设置为 ADC。

我有以下问题。

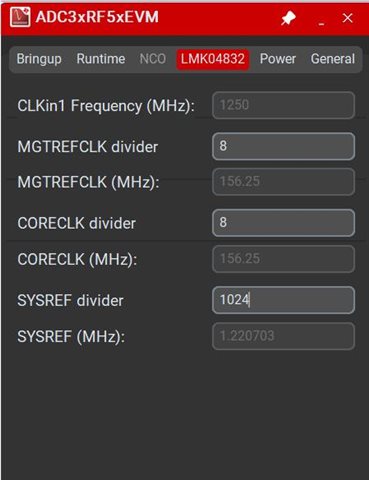

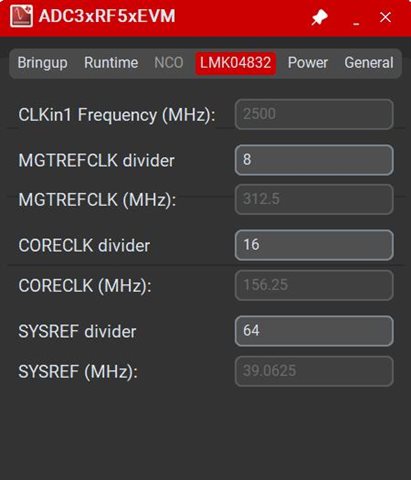

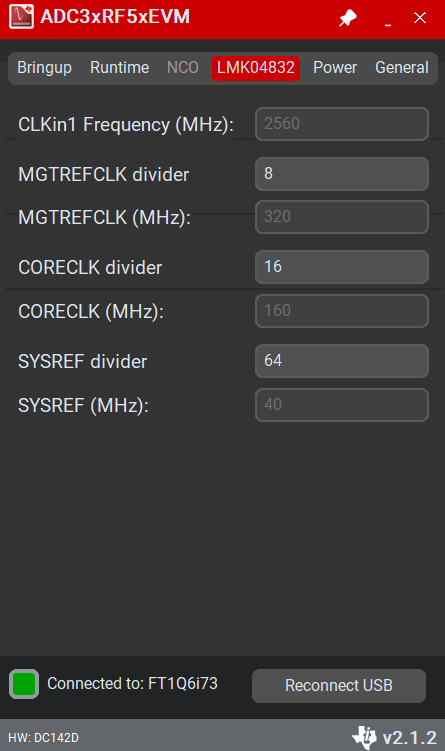

① 我想使用原始实现运行 FPGA、但 BringUP 时、LMK 设置中的分频器值会自动变为 8/16/64。 在这种情况下、我是否必须更改接收器 (FPGA)?

为什么在 BringUP 期间强制使用该值? ADC32RF55 侧是否受到限制? 还是特定于 EVM 的约束?

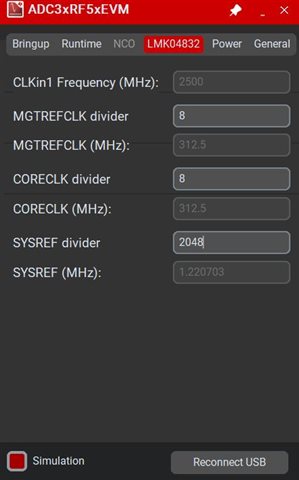

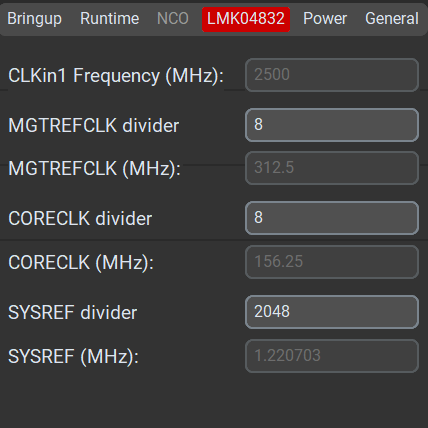

② 我知道如果在 BringUP 之后更改 LMK 页面的值、SYSREF 等的值将发生更改。 例如、如果我想继续计算 2048年8月8日 处每个分频器的值、以下过程是否没有问题? 是否有任何其他必要的程序?

【程序】

・将 ADC 工具用于 DeviceBringUP

・Ω 将 LMK 设置为 2048年8月8日。

・将 FPGA 写入 TSW・・・EVM 评估板。

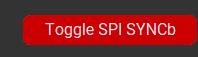

・按切换 SPI SYNCb。

③ 使用原始板运行 ADC32RF55 时、LMK 设置的分频器值是否应设计为在 BringUP 期间为 8/16/64? 我们是否应该从一开始就设计任意分频器值?

谢谢、此致、

Sayaka Kose