工具/软件:

大家好、

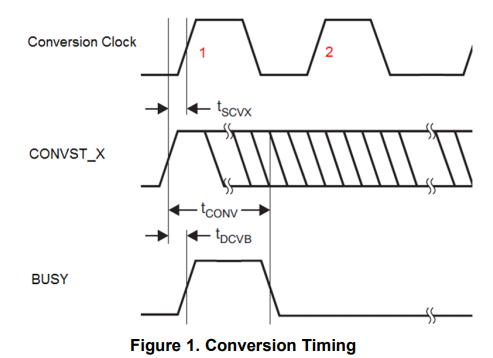

我来自 STM32 生态系统,我的问题是,与 ads8568 的连接,我只能运行一个大约 45MHz 的单一数据线 SPI 和高端 H7 系列,我可以达到 100 MHz。

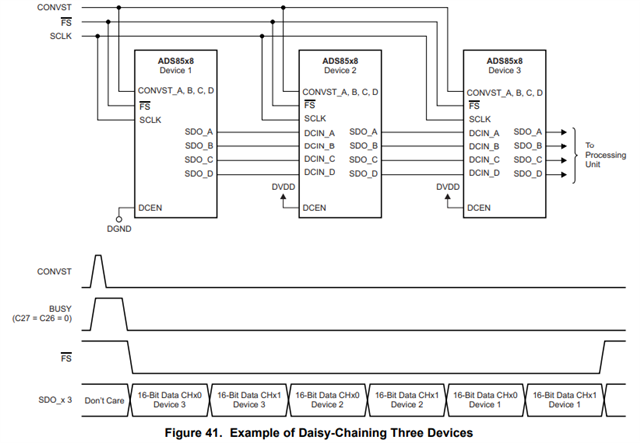

对于我的应用、我以菊花链方式运行三个 ADS8568、甚至运行 FPGA/CPLD、我仍然会受到 SPI 线路的限制。

此外、我想将数据存储在 SD 卡中、然后通过 LTE 模块将其推送到云端。

我假设要运行最大数据速率、只需连接一个 FPGA。

将 ADS8568 与 MCU 连接可以实现的最大采样速率是多少、推荐使用 SPI 通信方法吗?

提前感谢