工具/软件:

以下内容:

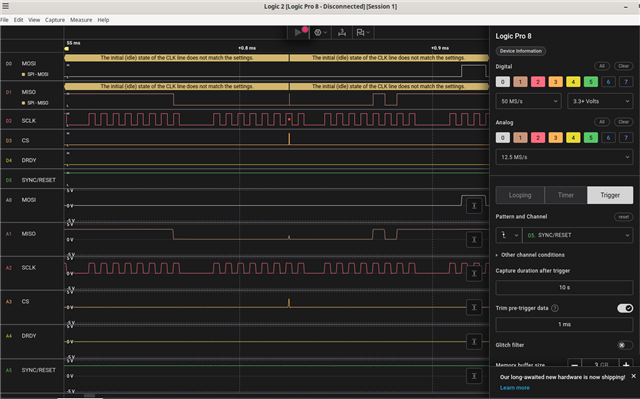

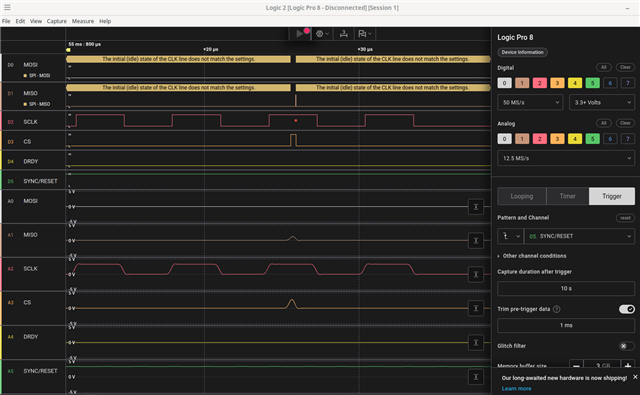

我们已经降低了 SCLK 的速度、但仍然存在问题。 如果您可以检查随附的萨莱会话转储、我想让您注意第一个 MOSI 通信以及其中表示的错误。 在+25µs 的某个地方。 你会发现在那里和奇数红色胆汁在 SCLK 信号,你也不会在 MISO 是一个比交通速度窄得多的胆汁。 似乎这可能是来自 CS 信号的串扰、还是我的眼睛在欺骗我? 逻辑分析仪声明“CLK 线路的初始 (IDLE) 状态与设置不匹配。“ 感谢您的任何智慧,你可以 share.e2e.ti.com/.../Session1.sal.zip

Clark