Other Parts Discussed in Thread: ADC12DJ5200RF, LMK04832, LMX2594

主题中讨论的其他器件: LMK04832、 LMX2594

工具/软件:

TI 团队大家好、

我目前正在调查中所述的 ADC12DJ5200RF JESD204C 实现所需的 CLK 和 sysref 频率。 我希望在选择这些时钟频率时得到一些帮助。 假设我使用 TI LMK04832 进行时钟分配、并使用 TI LMX2594 射频合成器来生成 ADC 内核频率和系统参考频率。

我的应用需要的一般流程是:10MHz INPUT(输入)-> LMK04832(输出)-> 10MHz CLK 和 10MHz SYSREF 输出(输出)-> LMX2594)-> 5200MHz CLK 至 ADC12DJ5200RF;2.539MHz SYSREF CLK 至 ADC12DJ5200RF。

对于 CLK、我计划使用源自 LMX2594 射频合成器的 5.2GHz 输入、以实现最大双通道采样率。 鉴于我的计算结果是 2.539MHz、我担心的是如何为 SYSREF 产生如此精确的时钟? 我在下面写下了我的计算。

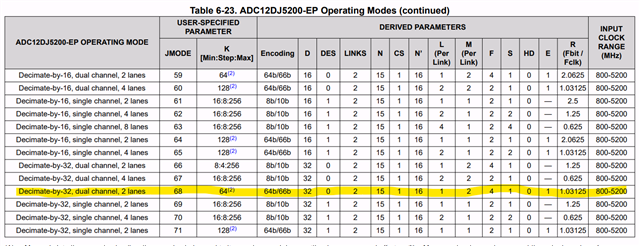

我们计划使用下面突出显示的 JESD 配置。 我们计划使用单稳态方法进行 JESD 同步。

fsysref =(R * fclk)/(66 * 33 * E * n)

fsysref =(1.03125 * 5200MHz)/(66 * 33 * 1 * 1)

fsysref = 2.539MHz

时钟是否接近、例如使用 2.5MHz、这是否重要? 我已经了解到、在 JESD 同步的单次触发方法中、相位同步比精确的系统参考频率更重要。

感谢您的任何帮助! 如果您有任何问题、敬请告知。

此致、

Joseph Blank