Other Parts Discussed in Thread: ADS1675, TXU0101

主题中讨论的其他器件: TXU0101

工具/软件:

你(们)好

我们有一个带有 ADS1675 的定制电路板、我们发现一个奇怪的问题:有时数据流中的两个样本会移位。 一个样本向左移动、下一个样本向右移动一位。 我们使用以下参数运行 ADS1675:

- MCLK= 20MHz

- 输出数据速率 2.5MHz

- DRATE 设置为“101"</s>“

- ll_config =高电平

- FPATH =低电平

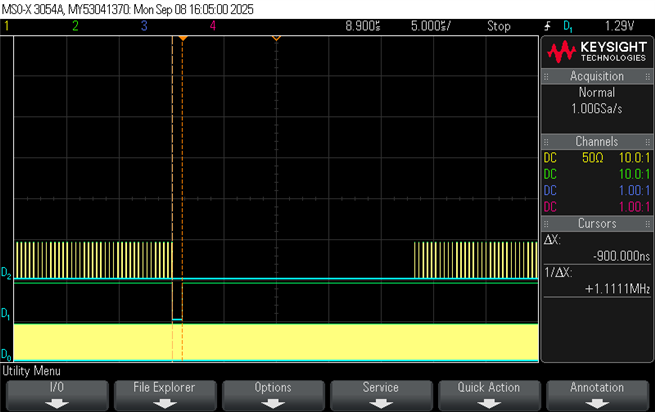

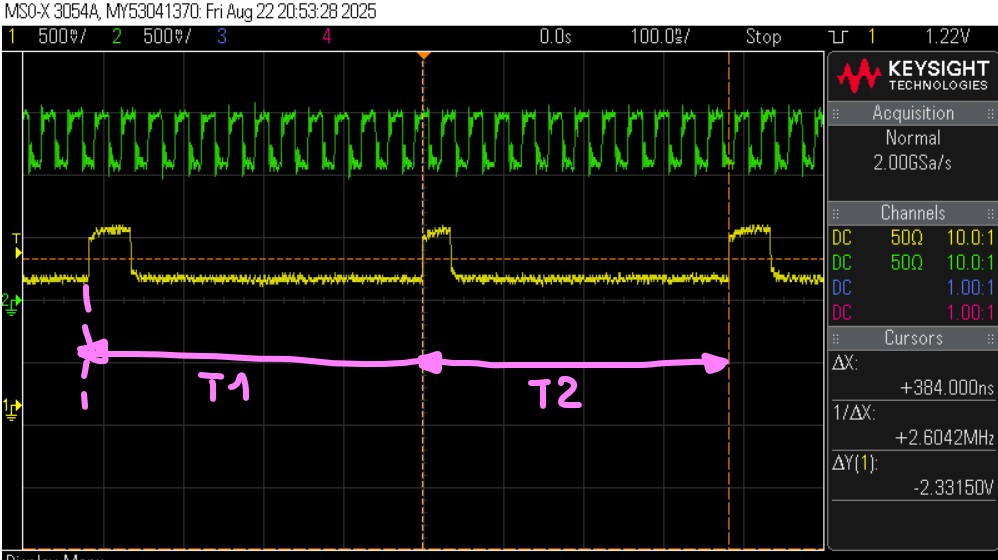

我们正在使用 FPGA 读取数据、我的第一个猜测是这肯定是 FPGA 的时序问题。 经过彻底调查后、发现 必须从 ADC 输出移位的数据:

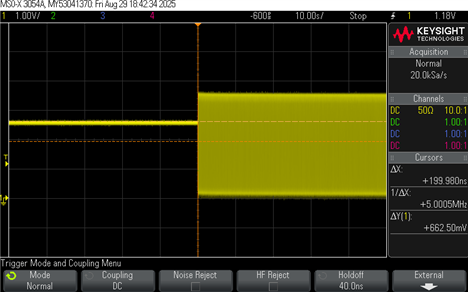

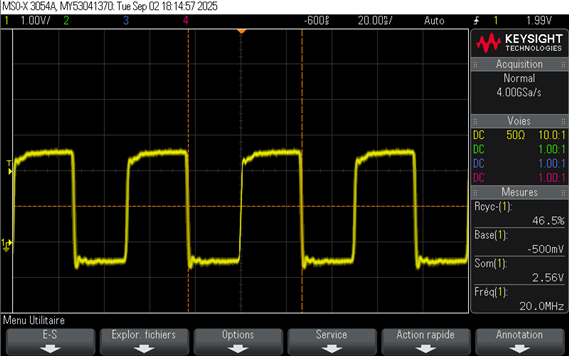

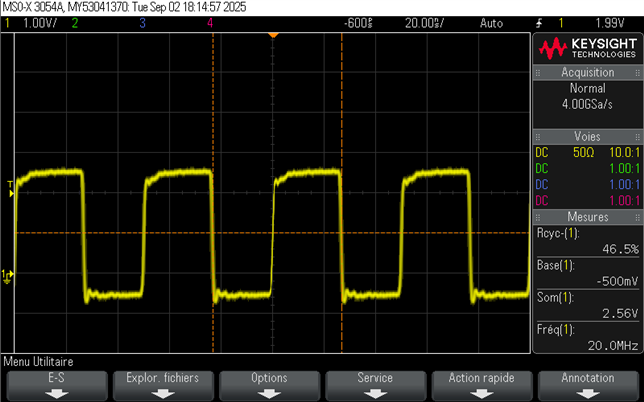

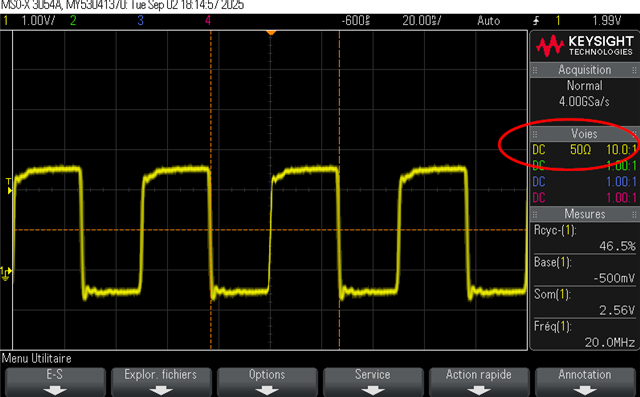

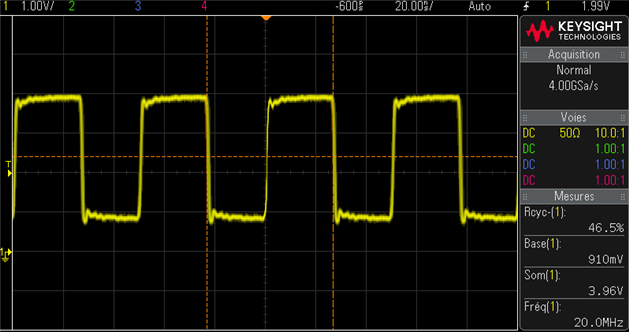

绿色通道 2 显示 SCLK div 2(除以 D-FF)、黄色通道是来自 ADC 的 DRDY 信号。 在正常运行期间、两个 DRDY 脉冲之间的周期为 400ns (@ 2.5MHz ODR)。 屏幕截图显示存在长周期 T1 = 416ns、具有 25 个时钟边沿、随后是 384ns 的短周期和 23 个时钟边沿。 这说明了两个错误的样本、一个左移、另一个右移。

我现在的问题是:什么会导致 ADS16575 这样的行为????

此致

返回