Other Parts Discussed in Thread: TI-JESD204-IP, ADC12QJ1600

主题中讨论的其他器件: ADC12QJ1600

工具/软件:

大家好、我有关于 TI-JESD204-IP 实现的一些简短问题、他在该领域的工作经验不足。

1.首先、我遇到了与此处所述问题 (e2e.ti.com/.../adc12qj1600evm-zcu102_8b10b-reference-design-not-showing-debug-cores) 类似的问题、其中调试内核在器件编程后不可见。 对这个问题的回复让我假设我需要一个由提供给 ADC 板 (ADC12QJ1600) 的信号发生器提供的有源外部时钟、这个时钟连接到我的 FPGA 以使这些内核可见、这是正确的还是可以在所提供的参考设计中解决?

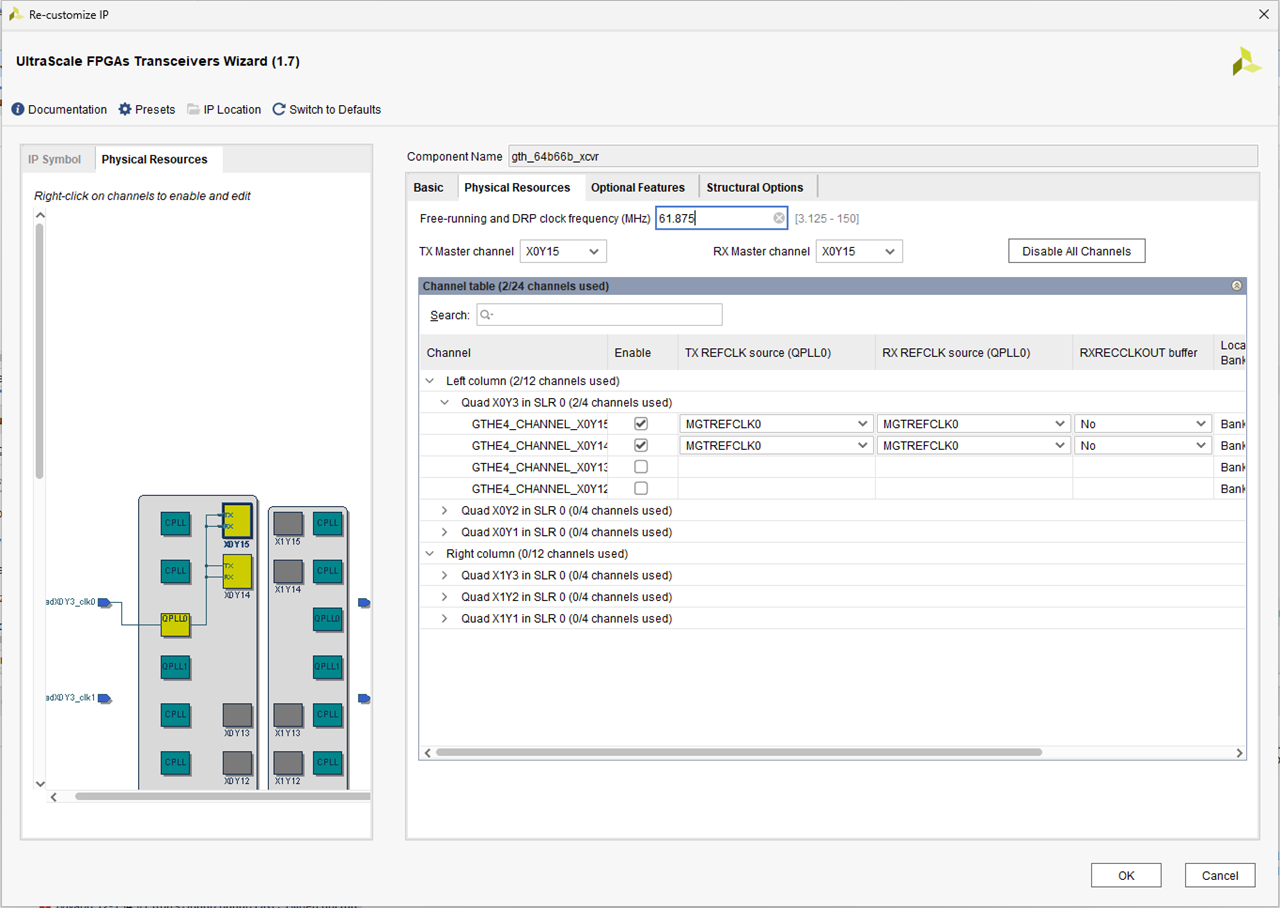

2.我还尝试了双路接收器配置。 我是否认为将收发器向导配置为两个通道(如下所示)那么简单、然后在相关文件中相应地将 NUMBER_OF_QUADS 设置为 1、将 NUMBER_TX_LANES、NUMBER_OF_RX_LANES、通道映射和通道极性值那么简单?

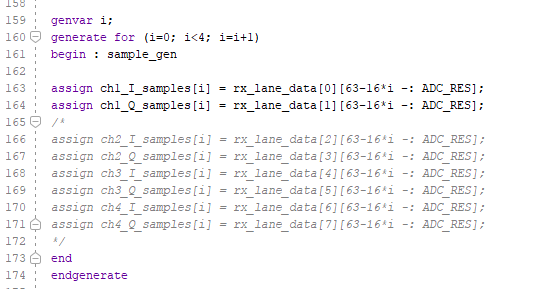

为了解决错误、我还需要省略 refdesign_rx.sv 文件中的以下代码部分。 我只是想确认这是否正确以及不会导致任何错误结果、因为我在 TI204c-IP 用户指南中未找到任何具体内容。

3.实施参考设计后,即使没有任何额外的定制,也有许多列出的警告(接近 1000 ),如下所示。 我是否可以假定这些可以忽略不计、因为我得到的印象是、对于不需要自定义的工作实现、不需要额外的工作?

谢谢你。