工具/软件:

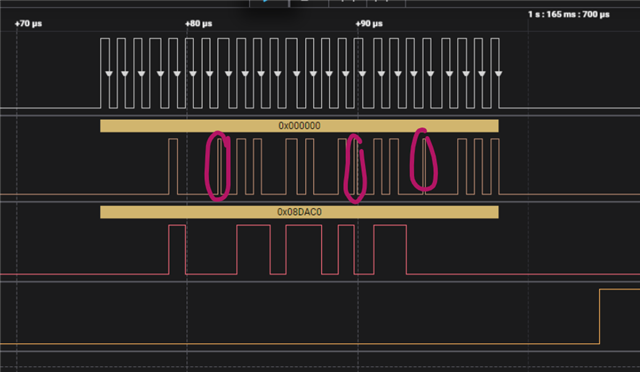

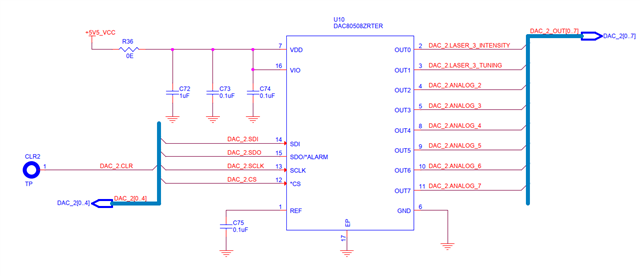

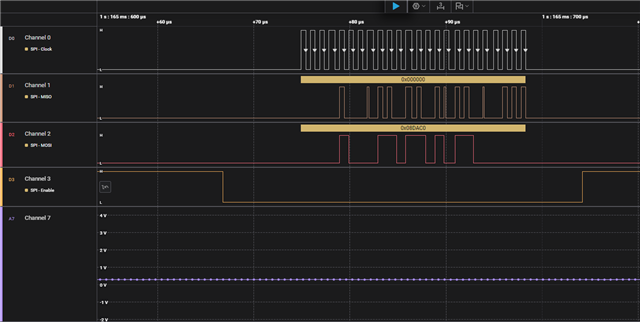

嘿,我正在使用 DAC80508ZRTER IC 和我得到的输出是不一致的: 当我输出一个常数值时它是有效的,但当我尝试输出一个斜坡或正弦波时,它要么倾向于保持在一个恒定值或随机值,在罕见的辛次上它给出了正确的信号。 原理图、代码、SPI 配置和信号输出与此开机自检一起连接。 我还有一个疑问、那就是、在编写 SDO 应该输出什么内容时? 因为目前我会得到随机值。

for (uint16_t i = 0;i < 65000;i+=1000)

{

dac8050x_writeDacReg (0、I);

HAL_DELAY (1000);

}

Bool dac8050x_writeDacReg(uint8_t channelNo、uint16_t 值)

{

Uint8_t tempBufferTransmit[NUM_FOUR]={init_zero};

tempBufferTransmit[NUM_ZERO]= 0x00 |(08 +通道编号);

tempBufferTransmit[NUM_ONE]=((uint16_t) value >> 8);

tempBufferTransmit[NUM_TWE]=((uint8_t) value);

返回 (dac8050x_writeRegister (tempBufferTransmit));

}